| 柤徧 |

MIRS1401丂僪乕僞儃乕僪徻嵶愝寁彂 |

| 斣崋 |

MIRS1401-ELEC-0002 |

| 斉悢 |

嵟廔峏怴擔 |

嶌惉 |

彸擣 |

夵掶婰帠 |

| A01 |

2014.12.8 |

塅嵅旤丄崅堜 |

|

弶斉 |

| A02 |

2014.12.19 |

塅嵅旤 |

|

僾儕儞僩婎斅梡偺幚憰恾傪捛壛 |

| B01 |

2015.2.2 |

塅嵅旤 |

戝徖愭惗 |

婎斅B偺巇條曄峏丅僾儕儞僩婎斅梡偺幚憰恾傪嶍彍 |

栚師

杮僪僉儏儊儞僩偼丄MIRS1401偱怴婯愝寁偟偨僪乕僞儃乕僪偺徻嵶愝寁彂偱偁傞丅

巊梡偡傞儌乕僞惂屼儃乕僪偲僄儞僐乕僟偑奺3屄偵丄僞僢僠僙儞僒偑9屄偵憹壛偟偨偙偲傪摜傑偊丄FPGA偺僺儞愝掕偲僪乕僞儃乕僪偺夞楬傪曄峏偟偨丅

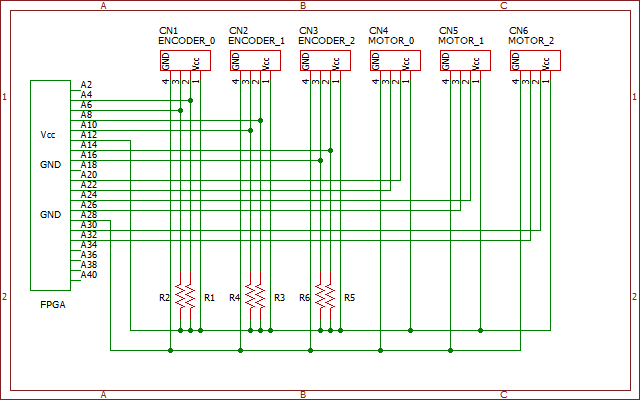

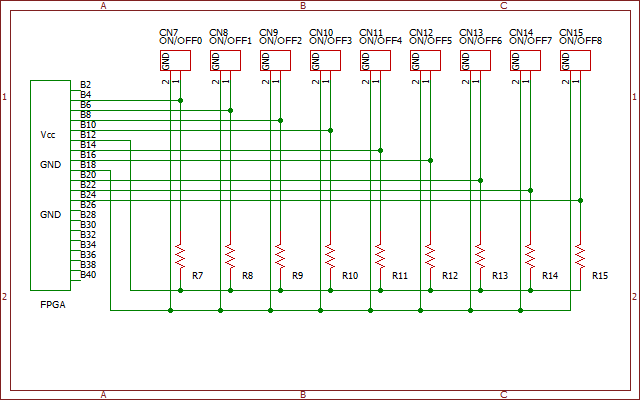

婎斅偼儌乕僞惂屼儃乕僪丒僄儞僐乕僟偵愙懕偝傟傞晹暘傪傑偲傔偨婎斅A偲丄僞僢僠僙儞僒偵偮側偑傞晹暘傪傑偲傔偨婎斅B偺2枃峔惉偲側偭偰偍傝丄偦傟偧傟曅柺IC僜働僢僩偵僼儔僢僩働乕僽儖傪嵎偟崬傒丄FPGA儃乕僪偲愙懕偡傞丅

側偍丄FPGA儃乕僪偺僺儞愝掕偺曄峏揰偼

FPGA僾儘僌儔儉徻嵶愝寁彂偵帵偡丅

僆儕僕僫儖僪乕僞儃乕僪偺嶌惉偵摉偨偭偰丄昗弨儃乕僪偐傜戝偒偔巇條曄峏傪峴偭偨揰傪帵偡丅

3.1. 婎斅A偺曄峏揰

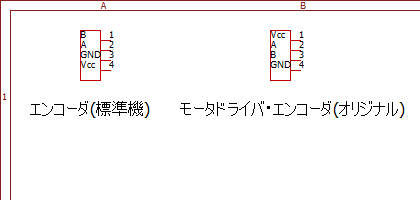

昗弨僪乕僞儃乕僪偱偼儌乕僞僪儔僀僶梡偺抂巕偲僄儞僐乕僟梡偺抂巕偺僺儞攝抲偑堎側偭偰偄偨偑丄杮儃乕僪偵偍偄偰偼僄儞僐乕僟偺抂巕傪儌乕僞僪儔僀僶偺僺儞攝抲偵崌傢偣偰摑堦偟偰偄傞丅偙傟傪恾1偵帵偡丅

傑偨丄昗弨婡偱偼儌乕僞惂屼儃乕僪偵庢傝晅偗傜傟偰偄偨僄儞僐乕僟梡偺僾儖傾僢僾掞峈偼丄婎斅A偵堏偟偰偄傞丅

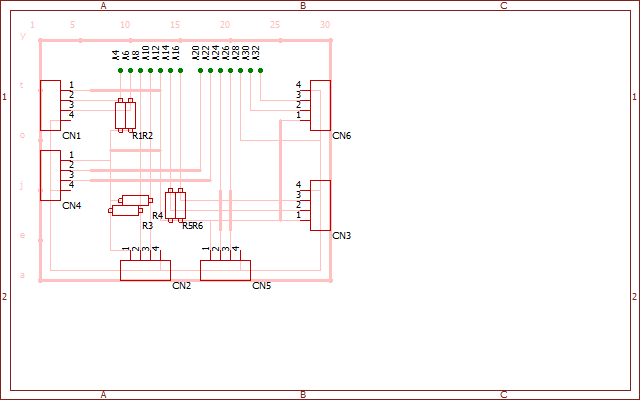

恾1丂僄儞僐乕僟偺僺儞攝抲偺曄峏揰

3.2. 婎斅B偺曄峏揰

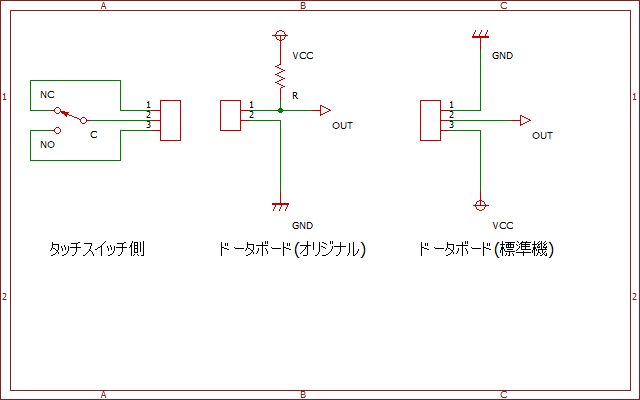

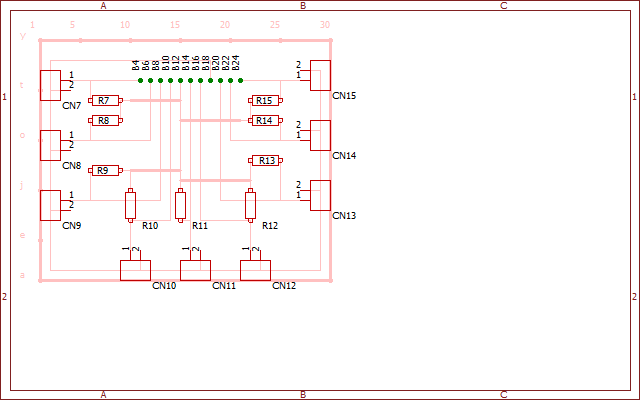

僪乕僞儃乕僪懁偺僞僢僠僗僀僢僠偺愙懕抂巕偼2僺儞偲側偭偰偄傞偑丄僞僢僠僗僀僢僠懁偼3僺儞偲側偭偰偄傞丅偙傟傪恾2偵帵偡丅

昗弨婡偺僪乕僞儃乕僪偲僞僢僠僗僀僢僠傪愙懕偟偨応崌丄僞僢僠僗僀僢僠懁偺愙懕僺儞傪岆偭偰攝慄偟偨応崌Vcc偲GND偑僔儑乕僩傪婲偙偡婋尟偑偁傞丅偙偺儕僗僋傪柍偔偡偨傔丄杮儃乕僪偼僾儖傾僢僾掞峈傪夘偟偰僔儑乕僩偑婲偙傜側偄峔憿偵曄峏偟偰偄傞丅

僪乕僞儃乕僪懁偺抂巕偺1斣偲僞僢僠僗僀僢僠懁偺1斣丄僪乕僞儃乕僪懁偺2斣偲僞僢僠僗僀僢僠懁偺2斣傪愙懕偡傞偲丄僞僢僠僗僀僢僠偑墴偝傟偰偄側偄娫偼OUT偺揹埵偑Low丄墴偝傟偰偄傞娫偼High偵側傞丅僪乕僞儃乕僪懁偺1斣偲僞僢僠僗僀僢僠懁偺2斣丄僪乕僞儃乕僪懁偺2斣偲僞僢僠僗僀僢僠懁偺3斣傪愙懕偡傞偲丄僞僢僠僗僀僢僠偑墴偝傟偰偄側偄娫偼OUT偺揹埵偑High丄墴偝傟偰偄傞娫偼Low偵側傞丅

恾2丂僞僢僠僗僀僢僠偺僺儞偺曄峏揰

恾3丂婎斅A夞楬恾

恾4丂婎斅B夞楬恾

昞1丂婎斅A晹昳昞

| 婰崋 | 昳柤丒婯奿 | 悢検 | 旛峫 |

|---|

| R1乣R6 | 6.8k兌 1/4W 扽慺旂枌掞峈 | 6 | 僄儞僐乕僟梡僾儖傾僢僾掞峈 |

| CN1乣CN6 | 4pin僐僱僋僞 | 6 | |

| - | 娵僺儞IC僜働僢僩 | 揔愰 | FPGA愙懕晹梡 |

| - | 儐僯僶乕僒儖婎斅 95亊72mm | 1 | |

昞2丂婎斅B晹昳昞

| 婰崋 | 昳柤丒婯奿 | 悢検 | 旛峫 |

|---|

| R7乣R15 | 6.8k兌 1/4W 扽慺旂枌掞峈 | 9 | 僞僢僠僗僀僢僠梡僾儖傾僢僾掞峈 |

| CN7乣CN15 | 2pin僐僱僋僞 | 9 | |

| - | 娵僺儞IC僜働僢僩 | 揔愰 | FPGA愙懕晹梡 |

| - | 儐僯僶乕僒儖婎斅 95亊72mm | 1 | |

恾偺懢慄晹偼婎斅偺昞柺偵働乕僽儖傪庢傝晅偗偰攝慄偡傞丅

恾5丂婎斅A幚憰恾

恾6丂婎斅B幚憰恾

奺抂巕丄IC僜働僢僩偵僥僗僞傪摉偰偰丄埲壓偵帵偡傛偆偵奺抂巕娫偑摫捠偟偰偄傞偐傪妋擣偡傞丅師偵丄偦傟埲奜偺抂巕偺娫偱僔儑乕僩偑婲偒偰偄側偄偐傪妋擣偡傞丅

婎斅A

- A12偲CN1乣6偺1斣(Vcc)

- A28偲CN1乣6偺4斣(GND)

- A4偲CN1偺2斣

- A6偲CN1偺3斣

- A8偲CN2偺2斣

- A10偲CN2偺3斣

- A14偲CN3偺2斣

- A16偲CN3偺3斣

- A20偲CN4偺2斣

- A22偲CN4偺3斣

- A24偲CN5偺2斣

- A26偲CN5偺3斣

- A30偲CN6偺2斣

- A32偲CN6偺3斣

婎斅B

- B28偲CN7乣15偺2斣(GND)

- B4偲CN7偺1斣

- B6偲CN8偺1斣

- B8偲CN9偺1斣

- B10偲CN10偺1斣

- B14偲CN11偺1斣

- B16偲CN12偺1斣

- B20偲CN13偺1斣

- B22偲CN14偺1斣

- B22偲CN15偺1斣

徖捗岺嬈崅摍愱栧妛峑丂揹巕惂屼岺妛壢