|

MIRS2008 FPGA製造仕様書 |

|

MIRS0801-ELEC-0002 |

|

版数 |

最終更新日 |

作成 |

承認 |

改訂記事 |

|

A01 |

2008/12/21 |

濁川 |

和泉 |

|

目次

1. 本ドキュメントについて

2. FPGAの変更点

2.1:PIC用信号回路

2.2:アドレスデコーダーの変更

2.3:ソフトウェアビジビリティ

1. 本ドキュメントについて

このドキュメントは、MIRS0801のFPGAの変更点を示すものである。

2. FPGAの変更点

MIRS本体に搭載したVFD回路に3bitの制御信号(以下PIC用信号)を送るための回路(PIC用信号回路)を新たに作成する。

FPGAのピン割り当てはエレクトロニクス詳細設計書参照。

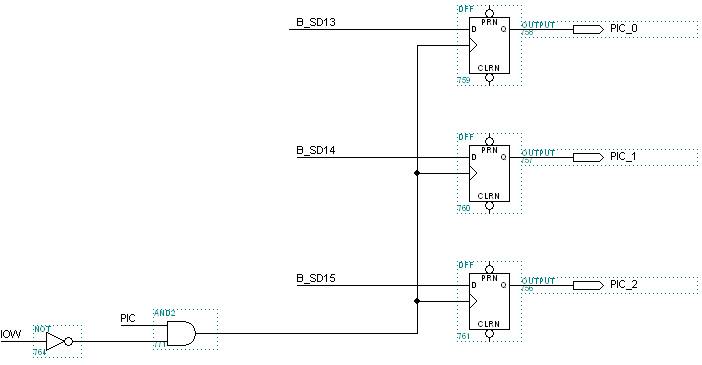

2.1:PIC用信号回路

回路図を下図に示す。

2.2:アドレスデコーダーの変更

アドレスデコーダーを下図に示す。

MIRS0801では使用しない「IRS_CODE3」をPIC用信号回路のアドレスに設定する。

2.3:ソフトウェアビジビリティ

|

名称 |

IO port Address [hex] |

R/W |

Port Name |

機能 |

||||||

|

PIC信号 |

0154 |

W |

PIC |

PIC用信号の入力 このアドレスに書き込むことにより、VFD回路に3bitのデータを出力する。 3bitのデータについてはエレクトロニクス詳細設計書参照。

|

|

関連文書 |

・ MIRS0701 システム提案書(MIRS0801-DSGN-0001)

・ MIRS0701 システム基本設計書(MIRS0801-DSGN-0002)

・ MIRS0801システム詳細設計書(MIRS0801-ELEC-0001)