|

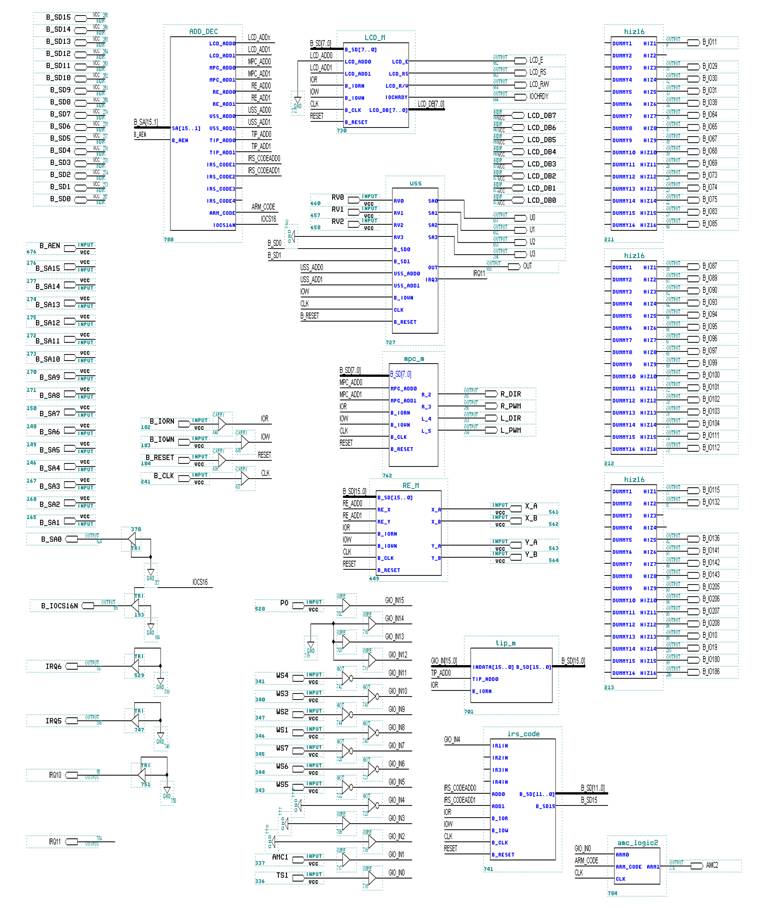

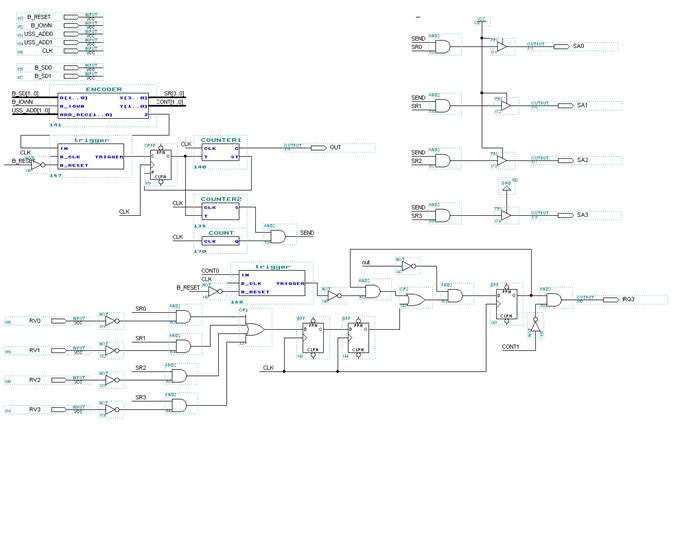

2.2. USSの変更

MIRS0802では、USSポートを3箇所しか使用しないため、残りの1箇所を入力、出力ともにハイインピーダンス状態に変更した。

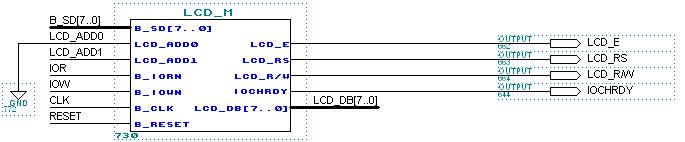

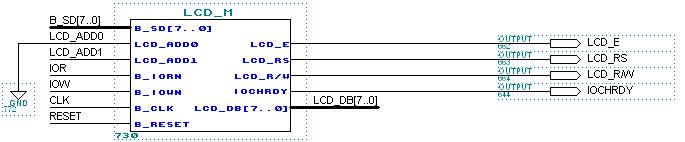

2.3. LCD_Mの変更

MIRS0802では、LCDを使用しないので、LCD_ADD0にGNDを接続しLCD_Mが動作しないようにした。

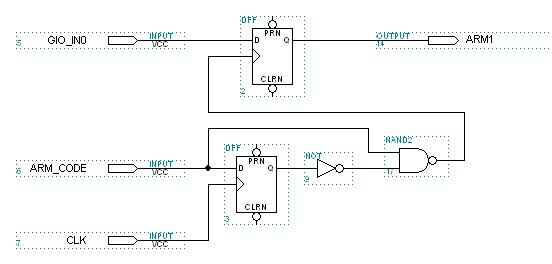

2.4. ADD_DECの変更

MIRS0802では、アーム制御用の回路を新たに作成したため、それに伴いADD_DEC内にARM_CODEを追加した。

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY ADD_DEC IS

PORT

(

SA :

IN STD_LOGIC_VECTOR(15

DOWNTO 1);

B_AEN :

IN STD_LOGIC;

LCD_ADD0,LCD_ADD1 : OUT STD_LOGIC;

MPC_ADD0,MPC_ADD1 : OUT STD_LOGIC;

RE_ADD0,RE_ADD1 :

OUT STD_LOGIC;

USS_ADD0,USS_ADD1 : OUT STD_LOGIC;

TIP_ADD0,TIP_ADD1 : OUT STD_LOGIC;

IRS_CODE1 :

OUT STD_LOGIC;

IRS_CODE2 :

OUT STD_LOGIC;

IRS_CODE3 :

OUT STD_LOGIC;

IRS_CODE4 :

OUT STD_LOGIC;

ARM_CODE :

OUT STD_LOGIC;

IOCS16n :

OUT STD_LOGIC

);

END ADD_DEC;

ARCHITECTURE DATAFLOW OF

ADD_DEC IS

signal

add : std_logic_vector(15 downto 0);

BEGIN

add <= SA & B_AEN;

LCD_ADD1 <= SA(1);

PROCESS (SA,B_AEN)

BEGIN

CASE

add IS

WHEN

"0000000100000000"

|"0000000100000010"

=>LCD_ADD0 <=

'1';

MPC_ADD0 <=

'0';

MPC_ADD1 <=

'0';

RE_ADD0 <=

'0';

RE_ADD1 <=

'0';

USS_ADD0 <=

'0';

USS_ADD <=

'0';

TIP_ADD0 <=

'0';

TIP_ADD1 <=

'0';

IRS_CODE1 <=

'0';

IRS_CODE2 <=

'0';

IRS_CODE3 <=

'0';

IRS_CODE4 <=

'0';

ARM_CODE <=

'0';

IOCS16n <=

'1';

〜中略〜

WHEN

OTHERS => LCD_ADD0 <=

'0';

MPC_ADD0

<=

'0';

MPC_ADD1

<=

'0';

RE_ADD0 <=

'0';

RE_ADD1 <=

'0';

USS_ADD0

<=

'0';

USS_ADD1

<=

'0';

TIP_ADD0

<=

'0';

TIP_ADD1

<=

'0';

IRS_CODE1 <= '0';

IRS_CODE2

<= '0';

IRS_CODE3 <= '0';

IRS_CODE4

<= '0';

ARM_CODE <=

'0';

IOCS16n <=

'0';

END

CASE;

END PROCESS;

END DATAFLOW;

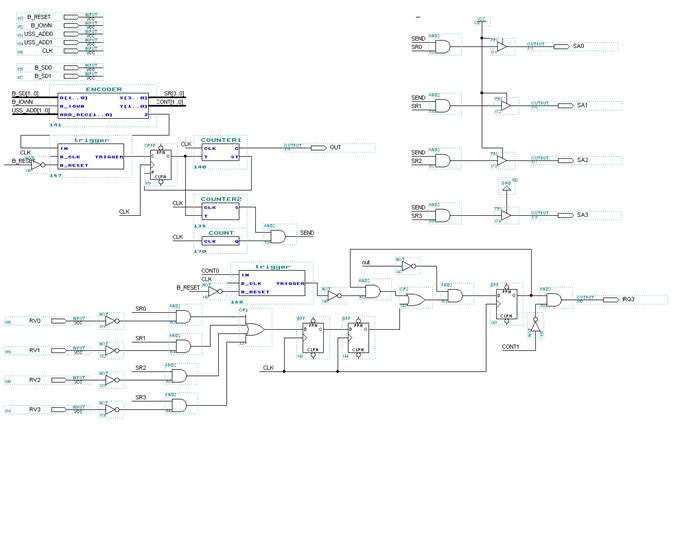

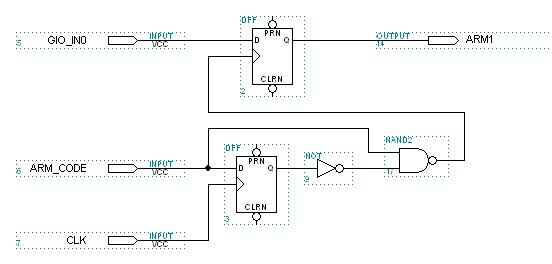

3. ARM制御回路の増設

3.1. ARM制御回路

MIRS0802では、アームを使用するので、そのアームを制御するための回路を設計した。

アーム制御用の回路とはなっているが、大本は、アーム制御用ボードで行うので、この回路の出力としては信号を送るだけである。

IRS用のピン設定をアームの入力用に使用するよう変更した。

|