4.5 その他回路

ここではそれらの説明を行う。

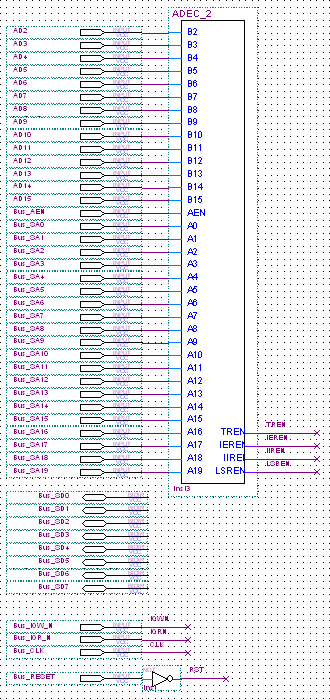

まず、Fig.1に示す回路はISAに接続するための仕組みである。

アドレスデコーダ部、データ部、制御線から構成されている。

アドレスデコーダ部はISAバスのアドレス信号からどのレジスタを有効にするのかを決めている部分である。

本体ならば4byteの選択なので2bitで十分だったが、通信回路単体でFPGAに書込み、デバッグできるように20bitのアドレス線全てを有効にしている。

データ部はISAバスの信号線(8bit)を橋渡ししている。

制御線はCLK、RESET、IOR、IOWの4本であり、それぞれIOR、IOWがActiveになることで、アドレスデコーダ部で選択されたレジスタに読み込み/書き込みが行われる。

なお、IOR、IOWは負論理なので注意。

RESETはISAバスのハードウェアリセットで、電源投入時に一定時間Activeになる。

なお、RESETは正論理である。

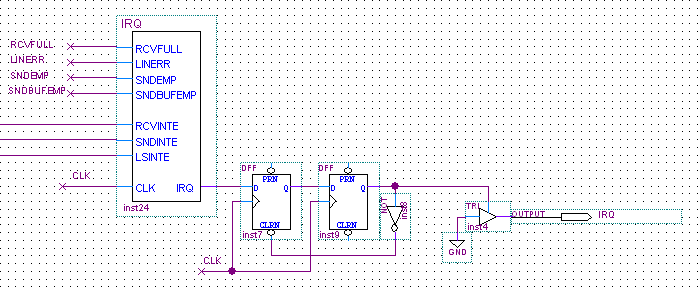

次に、Fig.2に示す回路は、割込みをISAバスの仕様に則って出力するためのものである。

IERの各割込み許可信号とそれに対応する各割込み発生要因とのANDを取り、それらのORを取ることで複数ある割込み要因からたった一つの割込み信号を作り出している。

また、出力に並べられたD-FF×2は、受信エラーが発生した際などに、「正常に動作を終了した」割込みと「受信したデータが不正であった」割込みなど、同時に発行される二つの割込みを一つに纏める役目がある。

なお、ISAバスの仕様では割込み信号はActive-Low、Non Active時はハイインピーダンスとされている。

Fig.1 ISAバス接続部

Fig.2 IRQ