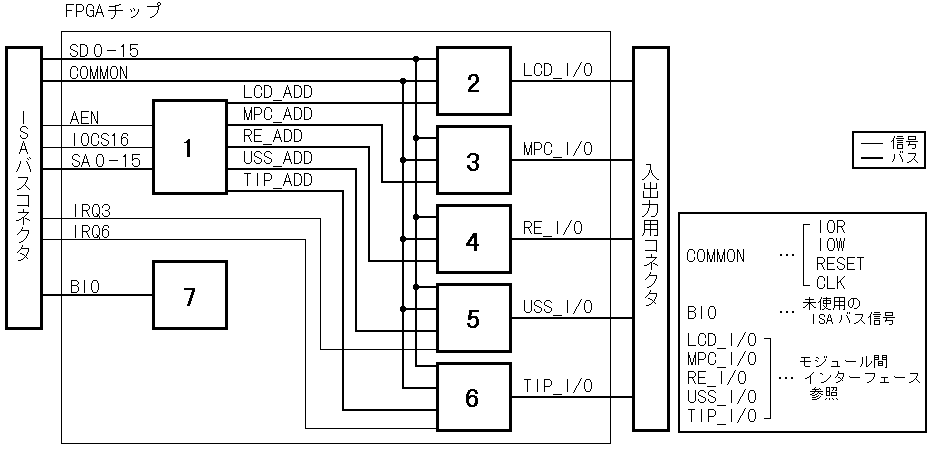

- 回路構成図

- 回路部品機能性能概略

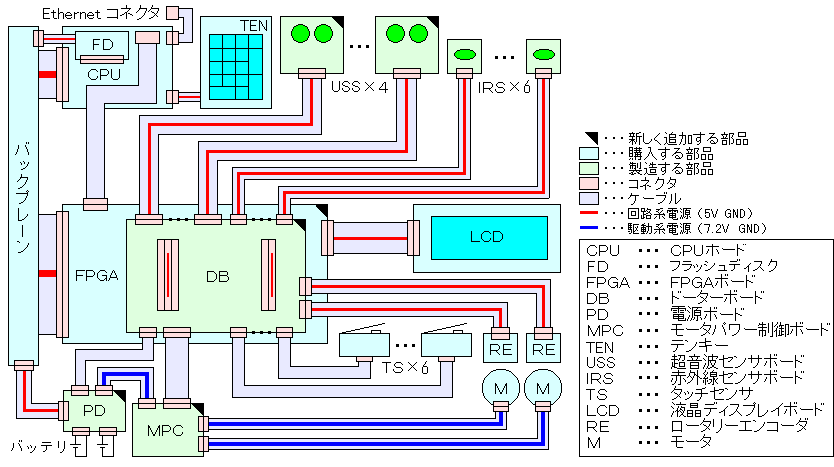

- システムの基本部分としてPC/AT互換のパーソナルコンピュータを使用する。

- バックプレーンとして4スロットのISAバスを使用する。

- イーサネットケーブルを使用してネットワークに接続することができる。

- ATLMIRS固有の入出力機能の制御をFPGAボードとドーターボードによって実現する。

- ATLMIRSで使用する全ソフトウェア、及びFPGAボードの回路情報は全てフラッシュディスクに保存する。

- センサ機能として6個のタッチセンサ、6個の赤外線センサ、4個の超音波センサ、2個のロータリーエンコーダを有する。

- マンマシンインターフェースの入力装置としてテンキー、出力装置として液晶ディスプレイを有する。

- 駆動系の速度制御をPWM制御によって行う。

- 電源として7.2Vニッカド充電電池2個を使用し、その内のひとつは+5Vに変換してから回路系電源として電子回路部に供給し、もうひとつは駆動系電源として7.2Vのまま緊急停止機能を介してモータに供給する

Figure.2_a 回路構成図 (signal.png)

| バックプレーン(AT-09-4T) |

| CPUボード(AMD80486DX5) |

| FPGAボード(D40-10-208) (*注 1) |

| 液晶ディスプレイボード (*注 2) |

*注 2 組立キットを購入し組立を行う

新しく製造する回路部品

| FPGAボード(D40-10-208) (*注 1) |

| 超音波センサ信号処理回路 |

| ドーターボード |

標準MIRSから流用する回路部品

| 赤外線センサボード |

| タッチセンサ(マイクロスイッチ) |

| ロータリーエンコーダ |

| モータ |

- 仕様

| 名称 |

NEAT-460 |

| CPU |

AMD80486DX5 |

| CLOCK |

133MHz |

| 外形寸法 |

142mm x 183mm |

| 販売元 |

日本データシステム株式会社 |

※詳細仕様は取扱説明書参照。

- 機能概要

- タッチセンサ信号の処理

- 赤外線センサ信号の処理

- パワーオン信号の処理

- 超音波センサ信号の処理

- ロータリーエンコーダ信号の処理

- 液晶表示ディスプレイ制御信号の処理

- モータパワー制御信号の処理

- ハードウェア割り込み処理

- 上記の各入出力機能の制御

- モジュール間インターフェース

- ISA バス

ISA バスのインターフェースについては ISA バスの仕様書、およびマイコンビルダーの仕様書を参照のこと。 - アドレスデコーダ

Table.7_c_2 アドレスデコーダのインターフェース 信号名 I/O 機能 SA 0 to 15 IN 16bit アドレスバス AEN IN アドレス開放 IOCS16 OUT 16bit I/Oサイクルに 1 ウェイトで応答 ADD_LCD OUT LCD_Mセレクタ信号 ADD_MPC OUT MPC_Mセレクタ信号 ADD_RE OUT RE_Mセレクタ信号 ADD_USS OUT USS_Mセレクタ信号 ADD_TIP OUT TIP_Mセレクタ信号 - 液晶ディスプレイ制御モジュール

Table.7_c_3 液晶ディスプレイ制御モジュールのインターフェース 信号名 I/O 機能 SD 0 to 15 IN 16bit データバス IOR IN I/Oリード・ストローブ IOW IN I/Oライト・ストローブ RESET IN システム・リセット CLK IN システム・クロック 8MHz デューティ50% RS OUT レジスタ・セレクト R/W OUT リード・ライト E OUT イネーブル信号 DB 0 to 7 INOUT 入出力データ - 入出力コネクタ

入出力コネクタのインターフェースはFPGAボード - ドーターボード間物理インターフェースを参照。 - ソフトウェアビジビリティ

- 液晶ディスプレイ制御モジュール

Table.7_d_1_1 液晶ディスプレイ制御モジュールのソフトウェアビジビリティ アドレス D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 R/W 機能説明 0100H * * * * * * * * 0 0 0 0 0 0 0 1 W 表示画面をクリア後、アドレスカウンタにDD RAMの0番地をセットする。 * * * * * * * * 0 0 0 0 0 0 1 * W アドレスカウンタにDD RAMの0番地をセットする。

シフトしていた表示も元に戻るが、この時DD RAMの内容は変化しない。* * * * * * * * 0 0 0 0 0 1 I/D S W データ書き込みおよびデータ読み出し時にカーソルの進む方向、

表示をシフトするかどうかの設定を行う。* * * * * * * * 0 0 0 0 1 D C B W 全表示のON/OFF(D)、カーソルのON/OFF(C)、

カーソル位置の文字のブリンク(B)をセットする。* * * * * * * * 0 0 0 1 S/C R/L * * W DD RAMの内容を変えずカーソルの移動、表示のシフト動作を行う。 * * * * * * * * 0 0 1 DL N F * * W インターフェース長(DL)、表示桁数(N)、文字フォント(F)を設定する。 * * * * * * * * 0 1 Acc W CG RAMのアドレスをセットする。この後送受するのはDD RAMのデータ。 * * * * * * * * 1 Add W DD RAMのアドレスをセットする。この後送受するのはDD RAMのデータ。 * * * * * * * * BF AC R 内部動作中を示すビジーフラグ(BF)およびアドレスカウンタの内容を読み出す。 0102H * * * * * * * * Write Data W DD RAMまたはCG RAMにデータを書き込む。 * * * * * * * * Read Data R DD RAMまたはCG RAMにデータを読み出す。

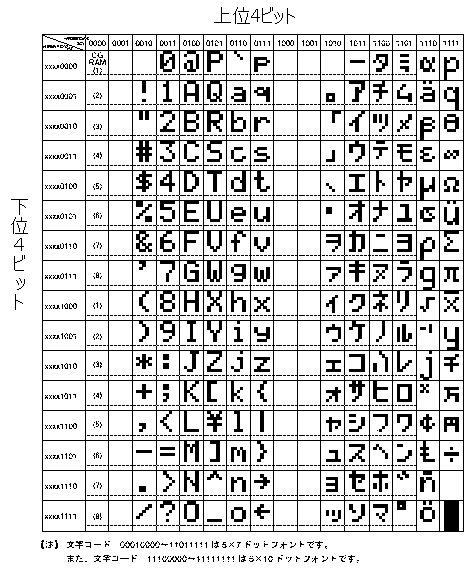

* I/D ・・・ '1' : インクリメント '0' : デクリメント * S ・・・ '1' : 表示のシフトを行う '0' : 表示のシフトを行わない * S/C ・・・ '1' : 表示のシフト '0' : カーソルの移動 * R/L ・・・ '1' : 右シフト * DL ・・・ '1' : 8bit '0' : 4bit * N ・・・ '1' : 2行目 '0' : 1行目 * F ・・・ '1' : 5 x 10ドット '0' : 5 x 7ドット * BF ・・・ '1' : 内部動作中 '0' : インストラクション受付可 * DD RAM ・・・ 表示データRAM * CG RAM ・・・ キャラクタジェネレータRAM * Acc ・・・ CG RAMのアドレス * Add ・・・ DD RAMのアドレス、カーソル番地に対応する * AC ・・・ DD RAM、CG RAMの両方に用いるアドレスカウンタ * Writeデータ , Readデータ ・・・ 以下の文字コード表を参照

Table.7_d_1_2 文字コード表

ATLMIRSではFPGAボードを使って以下の機能を実現する。

| 1. | アドレスデコーダ | : | 16bitのアドレスデータからモジュールセレクタ信号を作り出し、AEN信号に合わせて各モジュールに出力する。また、各モジュールが16bitのデータ入出力を行えるように IOCS16 信号を制御する。 |

| 2. | 液晶ディスプレイ制御モジュール | : | CPUから送られてくる8bitの液晶ディスプレイボード制御信号の出力制御を行う。 |

- 機能概要

- ドーターボードを通してFPGAボードにつながる各基板に電源(5V GND)を供給する。

- 液晶ディスプレイボードのコントラストアドジャストを行う。

- タッチセンサ(マイクロスイッチ)から入力されるスイッチ入力のチャタリング除去を行う。

- 超音波センサ選択信号によって選択された超音波センサをFPGAボードの超音波センサ信号処理モジュールに接続する。

- NEC製 IC μPD4701 を用いてロータリーエンコーダから送られるエンコード信号のカウントを行う。

- FPGAボードから送られてくるMPC信号を用いて、MPCボードのフォトカプラを動作させる。

- PDボードから送られてくる駆動系電源ON信号からパワーオン信号を作ってFPGAボードに出力する。

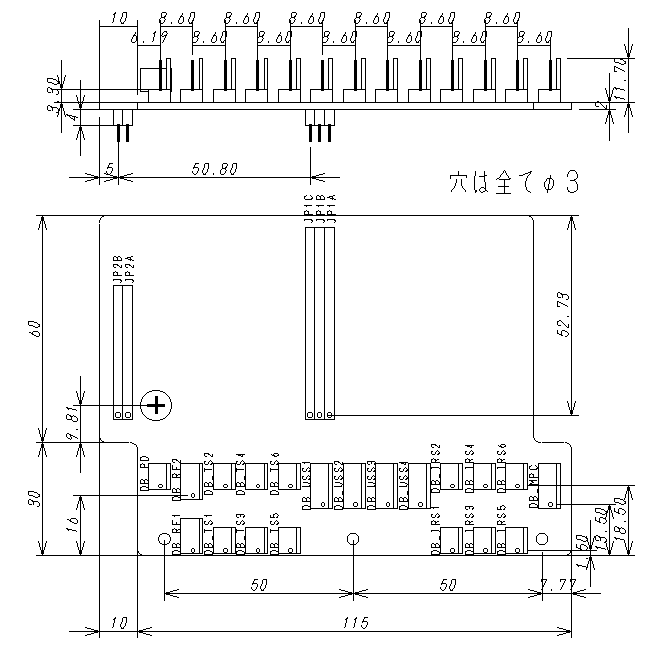

- 外形

| 1. | LCDコントラストアドジャスト回路 | : | ボリウムを用いてLCDボードの液晶ディスプレイのコントラストアドジャストを行う。また、その他の信号を素通りさせることでFPGAボードのジャンパとしての機能を持つ。 |

- 機能概要

- 外形

- 機能概要

赤外線センサボードの詳細は赤外線センサボード製造仕様書(MIRSDBMD-SBRD-0500)を参照。

- ISAラック

ISAラックのインターフェースはISAバス規格に準拠し、各基板を下表に示すようにバックプレーンに搭載する。 Table.16_a ISAラックへの基板の搭載方法 スロット.No ボード名称 備考 1 CPUボード 2 - 未使用 3 - 未使用 4 FPGAボード * スロットナンバーについてはバックプレーンの外観を参照。

- CPUボード - パーソナルコンピュータ

- 接続

CPUボードの CPU_UTP にイーサネットケーブルを接続する。

- 接続

- CPUボード - フラッシュディスク

- 接続

フラッシュディスクをCPUボードの CPU_IDE に挿入する。

- 接続

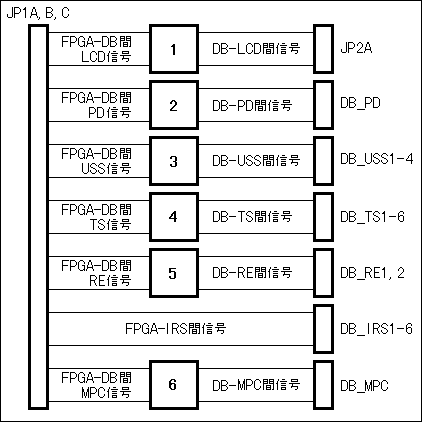

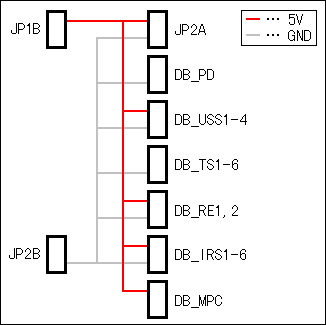

- FPGAボード - ドーターボード

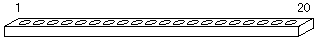

- コネクタ名称 : FPGA_JP20A (20pin ジャンパコネクタメス)

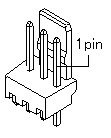

Figure.16_g_1 FPGA_JP20Aのコネクタ形状(jp20.png)

* コネクタの取りつけ位置、および方向はマイコンビルダー取扱説明書を参照。Table.16_g_1 FPGA_JP20Aのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 TS2 IN タッチセンサ信号 2 11 IRS1 IN 赤外線センサ信号 1 2 TS3 IN タッチセンサ信号 3 12 IRS2 IN 赤外線センサ信号 2 3 TS4 IN タッチセンサ信号 4 13 IRS3 IN 赤外線センサ信号 3 4 TS5 IN タッチセンサ信号 5 14 IRS4 IN 赤外線センサ信号 4 5 TS6 IN タッチセンサ信号 6 15 IRS5 IN 赤外線センサ信号 5 6 U0 OUT 超音波センサ送信信号。オープンコレクタ出力 16 IRS6 IN 赤外線センサ信号 6 7 U1 IN 超音波センサ受信信号 17 R_DIR OUT MPC 右方向信号。オープンコレクタ出力 8 US0 OUT 超音波センサ選択信号 0 18 R_PWM OUT MPC 右PWM信号。オープンコレクタ出力 9 US1 OUT 超音波センサ選択信号 1 19 L_DIR OUT MPC 左方向信号。オープンコレクタ出力 10 UTIM OUT 超音波センサ受信タイミング信号 20 L_PWM OUT MPC 左PWM信号。オープンコレクタ出力 - コネクタ名称 : DB_JP1A (20pin ジャンパコネクタオス)

Figure.16_g_2 DB_JP1Aのコネクタ形状(db_j20.png)

* コネクタの取りつけ位置、および方向はドーターボード外形図を参照。Table.16_g_2 DB_JP1Aのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 TS2 OUT タッチセンサ信号 2 11 IRS1 OUT 赤外線センサ信号 1 2 TS3 OUT タッチセンサ信号 3 12 IRS2 OUT 赤外線センサ信号 2 3 TS4 OUT タッチセンサ信号 4 13 IRS3 OUT 赤外線センサ信号 3 4 TS5 OUT タッチセンサ信号 5 14 IRS4 OUT 赤外線センサ信号 4 5 TS6 OUT タッチセンサ信号 6 15 IRS5 OUT 赤外線センサ信号 5 6 U0 IN 超音波センサ送信信号 16 IRS6 OUT 赤外線センサ信号 6 7 U1 OUT 超音波センサ受信信号 17 R_DIR IN MPC 右方向信号 8 US0 IN 超音波センサ選択信号 0 18 R_PWM IN MPC 右PWM信号 9 US1 IN 超音波センサ選択信号 1 19 L_DIR IN MPC 左方向信号 10 UTIM IN 超音波センサ受信タイミング信号 20 L_PWM IN MPC 左PWM信号 - コネクタ名称 : FPGA_JP30C (20pin ジャンパコネクタメス)

Figure.16_g_3 FPGA_JP30Cのコネクタ形状(jp20.png)

* コネクタの取りつけ位置、および方向はマイコンビルダー取扱説明書を参照。Table.16_g_3 FPGA_JP30Cのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 PO IN パワーオン信号 11 Vcc - 5V 2 TS1 IN タッチセンサ信号 1 12 Vcc - 5V 3 RE_D0 IN REカウントデータ 0 13 Vcc - 5V 4 RE_D2 IN REカウントデータ 2 14 Vcc - 5V 5 RE_D4 IN REカウントデータ 4 15 Vcc - 5V 6 RE_D6 IN REカウントデータ 6 16 Vcc - 5V 7 Vcc - 5V 17 Vcc - 5V 8 Vcc - 5V 18 Vcc - 5V 9 Vcc - 5V 19 Vcc - 5V 10 Vcc - 5V 20 Vcc - 5V - コネクタ名称 : DB_JP1B (20pin ジャンパコネクタオス)

Figure.16_g_4 DB_JP1Bのコネクタ形状(db_j20.png)

* コネクタの取りつけ位置、および方向はドーターボード外形図を参照。Table.16_g_4 DB_JP1Bのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 PO OUT パワーオン信号 11 Vcc - 5V 2 TS1 OUT タッチセンサ信号 1 12 Vcc - 5V 3 RE_D0 OUT REカウントデータ 0 13 Vcc - 5V 4 RE_D2 OUT REカウントデータ 2 14 Vcc - 5V 5 RE_D4 OUT REカウントデータ 4 15 Vcc - 5V 6 RE_D6 OUT REカウントデータ 6 16 Vcc - 5V 7 Vcc - 5V 17 Vcc - 5V 8 Vcc - 5V 18 Vcc - 5V 9 Vcc - 5V 19 Vcc - 5V 10 Vcc - 5V 20 Vcc - 5V - コネクタ名称 : FPGA_JP20B (20pin ジャンパコネクタメス)

Figure.16_g_5 FPGA_JP20Bのコネクタ形状(jp20.png)

* コネクタの取りつけ位置、および方向はマイコンビルダー取扱説明書を参照。Table.16_g_5 FPGA_JP20Bのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 RE_U/L OUT REカウントデータ上位・下位選択 11 R/W OUT LCD リード・ライト 2 RE_X/Y OUT RE Xカウンタ・Yカウンタ選択 12 E OUT LCD イネーブル 3 RE_CS OUT RE チップセレクト 13 DB0 INOUT LCD データ 0 4 RE_D1 IN REカウントデータ 1 14 DB1 INOUT LCD データ 1 5 RE_D3 IN REカウントデータ 3 15 DB2 INOUT LCD データ 2 6 RE_D5 IN REカウントデータ 5 16 DB3 INOUT LCD データ 3 7 RE_D7 IN REカウントデータ 7 17 DB4 INOUT LCD データ 4 8 RE_RY OUT RE Yカウンタリセット 18 DB5 INOUT LCD データ 5 9 RE_RX OUT RE Xカウンタリセット 19 DB6 INOUT LCD データ 6 10 RS OUT LCD レジスタセレクト 20 DB7 INOUT LCD データ 7 - コネクタ名称 : DB_JP1C (20pin ジャンパコネクタオス)

Figure.16_g_6 DB_JP1Cのコネクタ形状(db_j20.png)

* コネクタの取りつけ位置、および方向はドーターボード外形図を参照。Table.16_g_6 DB_JP1Cのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 RE_U/L IN REカウントデータ上位・下位選択 11 R/W IN LCD リード・ライト 2 RE_X/Y IN RE Xカウンタ・Yカウンタ選択 12 E IN LCD イネーブル 3 RE_CS IN RE チップセレクト 13 DB0 INOUT LCD データ 0 4 RE_D1 OUT REカウントデータ 1 14 DB1 INOUT LCD データ 1 5 RE_D3 OUT REカウントデータ 3 15 DB2 INOUT LCD データ 2 6 RE_D5 OUT REカウントデータ 5 16 DB3 INOUT LCD データ 3 7 RE_D7 OUT REカウントデータ 7 17 DB4 INOUT LCD データ 4 8 RE_RY IN RE Yカウンタリセット 18 DB5 INOUT LCD データ 5 9 RE_RX IN RE Xカウンタリセット 19 DB6 INOUT LCD データ 6 10 RS IN LCD レジスタセレクト 20 DB7 INOUT LCD データ 7 - コネクタ名称 : FPGA_JP60B (26pin ジャンパコネクタメス)

Figure.16_g_7 FPGA_JP60Bのコネクタ形状(jp26.png)

* コネクタの取りつけ位置、および方向はマイコンビルダー取扱説明書を参照。Table.16_g_7 FPGA_JP60Bのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 Vcc - 5V 14 DB7 INOUT LCD データ 7 2 GND - GND 15 - - 未使用 3 Vo - LCD コントラストアドジャスト 16 - - 未使用 4 RS IN LCD レジスタセレクト 17 - - 未使用 5 R/W IN LCD リード・ライト 18 - - 未使用 6 E IN LCD イネーブル 19 - - 未使用 7 DB0 INOUT LCD データ 0 20 - - 未使用 8 DB1 INOUT LCD データ 1 21 - - 未使用 9 DB2 INOUT LCD データ 2 22 - - 未使用 10 DB3 INOUT LCD データ 3 23 - - 未使用 11 DB4 INOUT LCD データ 4 24 - - 未使用 12 DB5 INOUT LCD データ 5 25 - - 未使用 13 DB6 INOUT LCD データ 6 26 - - 未使用 - コネクタ名称 : DB_JP2A (14pin ジャンパコネクタオス)

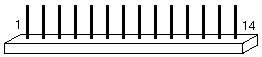

Figure.16_g_8 DB_JP2Aのコネクタ形状(db_j14.png)

* コネクタの取りつけ位置、および方向はドーターボード外形図を参照。Table.16_g_8 DB_JP2Aのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 Vcc - 5V 8 DB1 INOUT LCD データ 1 2 GND - GND 9 DB2 INOUT LCD データ 2 3 Vo - LCD コントラストアドジャスト 10 DB3 INOUT LCD データ 3 4 RS OUT LCD レジスタセレクト 11 DB4 INOUT LCD データ 4 5 R/W OUT LCD リード・ライト 12 DB5 INOUT LCD データ 5 6 E OUT LCD イネーブル 13 DB6 INOUT LCD データ 6 7 DB0 INOUT LCD データ 0 14 DB7 INOUT LCD データ 7 - コネクタ名称 : FPGA_JP60C (26pin ジャンパコネクタメス)

Figure.16_g_9 FPGA_JP60Cのコネクタ形状(jp26.png)

* コネクタの取りつけ位置、および方向はマイコンビルダー取扱説明書を参照。Table.16_g_9 FPGA_JP60Cのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 GND - GND 14 GND - GND 2 GND - GND 15 GND - GND 3 GND - GND 16 GND - GND 4 GND - GND 17 GND - GND 5 GND - GND 18 GND - GND 6 GND - GND 19 GND - GND 7 GND - GND 20 GND - GND 8 GND - GND 21 GND - GND 9 GND - GND 22 GND - GND 10 GND - GND 23 GND - GND 11 GND - GND 24 GND - GND 12 GND - GND 25 GND - GND 13 GND - GND 26 GND - GND - コネクタ名称 : DB_JP2B (14pin ジャンパコネクタオス)

Figure.16_g_10 DB_JP2Bのコネクタ形状(db_j14.png)

* コネクタの取りつけ位置、および方向はドーターボード外形図を参照。Table.16_g_10 DB_JP2Bのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 GND - GND 8 GND - GND 2 GND - GND 9 GND - GND 3 GND - GND 10 GND - GND 4 GND - GND 11 GND - GND 5 GND - GND 12 GND - GND 6 GND - GND 13 GND - GND 7 GND - GND 14 GND - GND - 接続

ドーターボードはFPGAボードの亀の子基盤となっているので、各ボードのコネクタが下表の対応関係になるようにドーターボードをFPGAボードに挿しこむ。 Table.16_g_11 FPGAボードコネクタとドーターボードコネクタの対応関係 FPGAボード ドーターボード JP20A <-> JP1A JP30C <-> JP1B JP20B <-> JP1C JP60B(1pin to 14pin) <-> JP2A JP60C(1pin to 14pin) <-> JP2B

- コネクタ名称 : FPGA_JP20A (20pin ジャンパコネクタメス)

- ドーターボード - タッチセンサ

- コネクタ名称 : DB_TSN (N =1 to 6) (MOLEX 5045-03A)

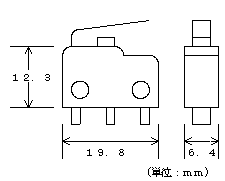

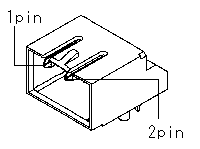

Figure.16_i_1 DB_TSN のコネクタ形状(5045a-03.png) Table.16_i_1 DB_TSN のインターフェース ピン.No 信号名 I/O 備考 1 GND - GND 2 TSON IN タッチセンサON信号 3 TSOF IN タッチセンサOFF信号 - コネクタ名称 : Micro Switch N (N =1 to 6)(omronSS-5GL)

Figure.16_i_2 Micro Switch N のコネクタ形状(ts.png) Table.16_i_2 Micro Switch N のインターフェース ピン.No 信号名 I/O 備考 1 GND - GND 2 TSON OUT タッチセンサON信号 3 TSOF OUT タッチセンサOFF信号 - 接続

3芯のフラットケーブルの両端を1本ずつ裂いてから片側に5051用ターミナルを圧着してMOLEX 5051ハウジングに挿入し、DB_TSN に挿入する。もう片側は絶縁ビニルを剥いてからマイクロスイッチにはんだ付けする。

接続時のピン対応は下表を参照。Table.16_i_3 DB_TSN と Micro Switch N のピン対応 DB_TS1 Micro Switch 1 DB_TS4 Micro Switch 4 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 1 GND <-> 1 GND 1 GND <-> 1 GND 2 TSON <-> 2 TSON 2 TSON <-> 2 TSON 3 TSOF <-> 3 TSOF 3 TSOF <-> 3 TSOF DB_TS2 Micro Switch 2 DB_TS5 Micro Switch 5 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 1 GND <-> 1 GND 1 GND <-> 1 GND 2 TSON <-> 2 TSON 2 TSON <-> 2 TSON 3 TSOF <-> 3 TSOF 3 TSOF <-> 3 TSOF DB_TS3 Micro Switch 3 DB_TS6 Micro Switch 6 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 1 GND <-> 1 GND 1 GND <-> 1 GND 2 TSON <-> 2 TSON 2 TSON <-> 2 TSON 3 TSOF <-> 3 TSOF 3 TSOF <-> 3 TSOF

- コネクタ名称 : DB_TSN (N =1 to 6) (MOLEX 5045-03A)

- 電源ボード - バッテリ

- コネクタ名称 : PD_CN1,2 (MOLEX 53259-0220)

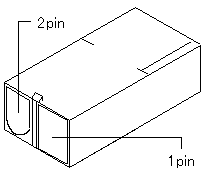

Figure.16_q_1 PD_CN1,2のコネクタ形状(53259-0220.png) Table.16_q_1 PD_CN1,2のインターフェース ピン.No 信号名 I/O 備考 1 Vin - +7.2 2 GND - GND - コネクタ名称 : バッテリコネクタ 1,2

Figure.16_q_2 バッテリコネクタ 1,2のコネクタ形状(battery.png) Table.16_q_2 バッテリコネクタ 1,2のインターフェース ピン.No 信号名 I/O 備考 1 Vin - +7.2V 2 GND - GND - 接続

電源ケーブルの片側は、バッテリコネクタのターミナルを圧着してバッテリコネクタハウジングに入れる。

もう片側はMOLEX 51067用ターミナルを圧着してからMOLEX 51067-0220ハウジングに挿入し、PD_CN1,2に挿入する。

接続時のピン対応は下表を参照。また、Vinには赤、GNDには黒の電源ケーブルを使用すること。Table.16_q_3 PD_CN1,2 とバッテリコネクタ 1,2のピン対応 PD_CN1 バッテリコネクタ 1 ピン.No 信号名 ピン.No 信号名 1 Vin <-> 1 Vin 2 GND <-> 2 GND PD_CN2 バッテリコネクタ 2 ピン.No 信号名 ピン.No 信号名 1 Vin <-> 1 Vin 2 GND <-> 2 GND

- コネクタ名称 : PD_CN1,2 (MOLEX 53259-0220)