- 行動制御機能(行動モードの遷移など)

- 各種行動機能

- 移動機能

- 走行制御機能

- 超音波探索機能

- 赤外センサ探知機能

- 白線検出機能

- 接触関知機能

- 制御系

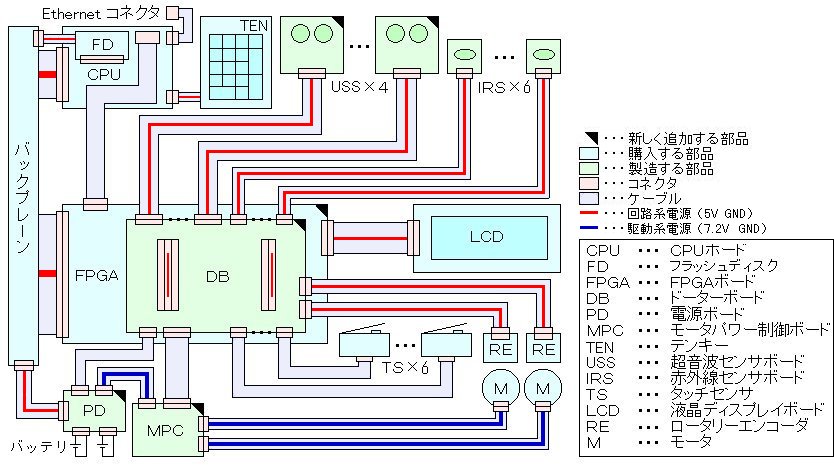

ハードウェア

CPU ボード i486 133MHz, Memory 16MB, SVGA chip, 10M Ethernet, ISA bus 記憶装置 Flush memory 64MB (IDE ディスク互換) FPGA ボード 標準ゲート数 10,000, RAMビット数:6,144, ユーザI/O数:134, ISA bus オペレーティングシステム

RT-Linux Ver 2.3 (Linux kernel 2.2.14)

- 駆動系

DC モータ 無負荷回転数:10300rpm, 停動トルク:218 mNm 最大連続トルク:24.2 mNm ギア ギア比:16:1 遊星ギア 最大効率:70% ロータリエンコーダ 100パルス 2チャンネル 出力信号:TTL コンパチブル PWM 制御 7.2V の duty 比を変化させて、実効電圧を変える方式 - センサー系

- 超音波センサ 4(標準)

- 赤外線センサ 6(標準)※

- タッチセンサ 6(標準)※

- 白線検出センサ ?

- 電力系

- ニッカド電池 7.2V (1700mAh) x 2

- 制御用 シリーズレギュレータにより 5V に変換

- 駆動用 7.2V

- マン・マシンインターフェイス

- テンキー (PS/2)

- LCD (16文字×2行)