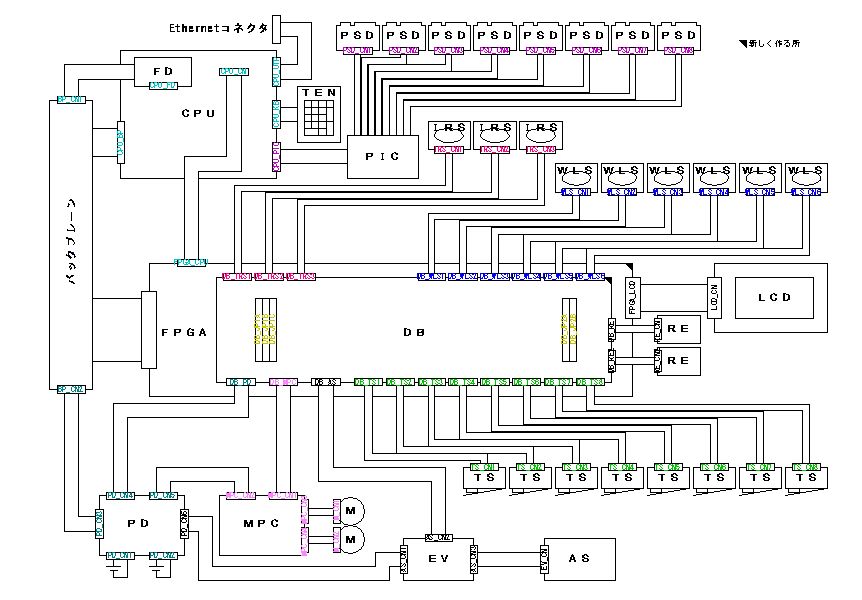

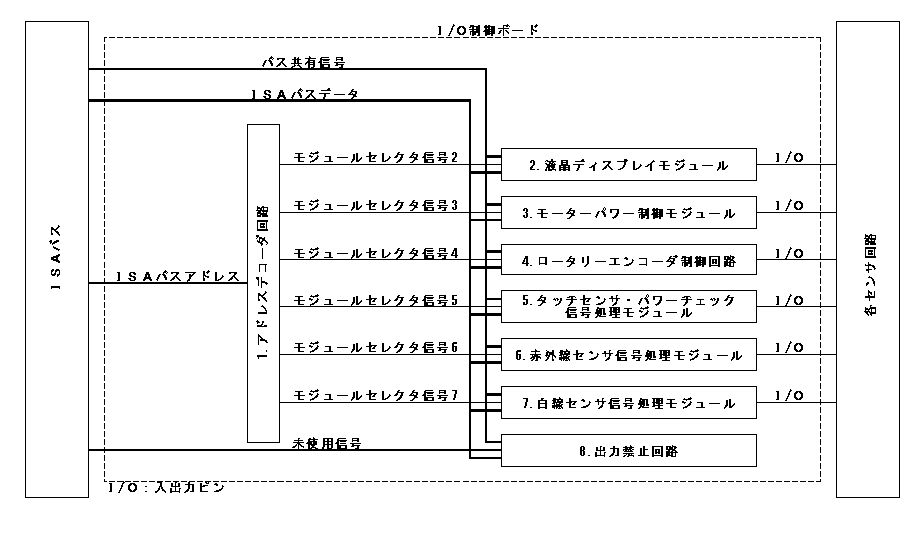

概略ブロック図

Fig.3_1_1に概略ブロック図を示す。

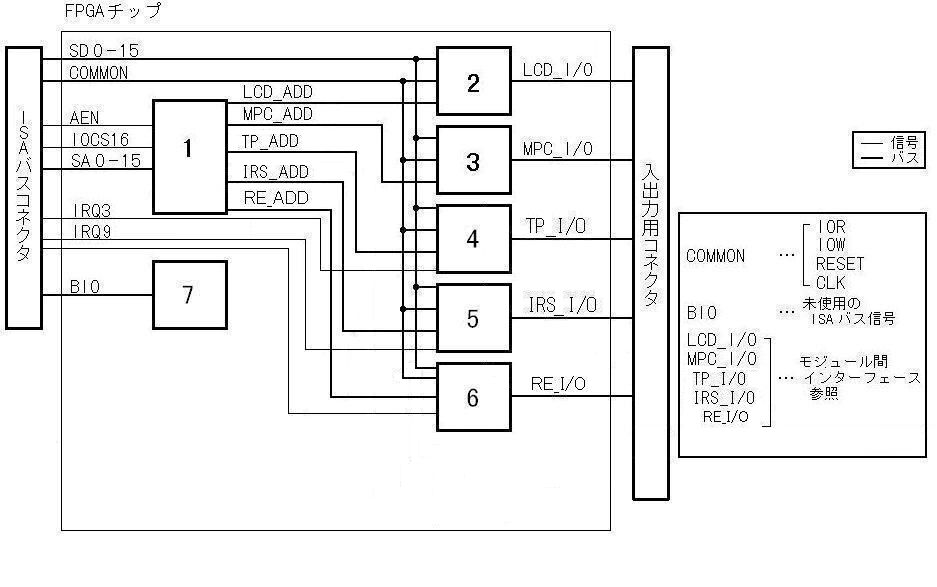

Fig.3_1_2にFPGA内部回路のブロック図を示す。

<各モジュールの詳細>

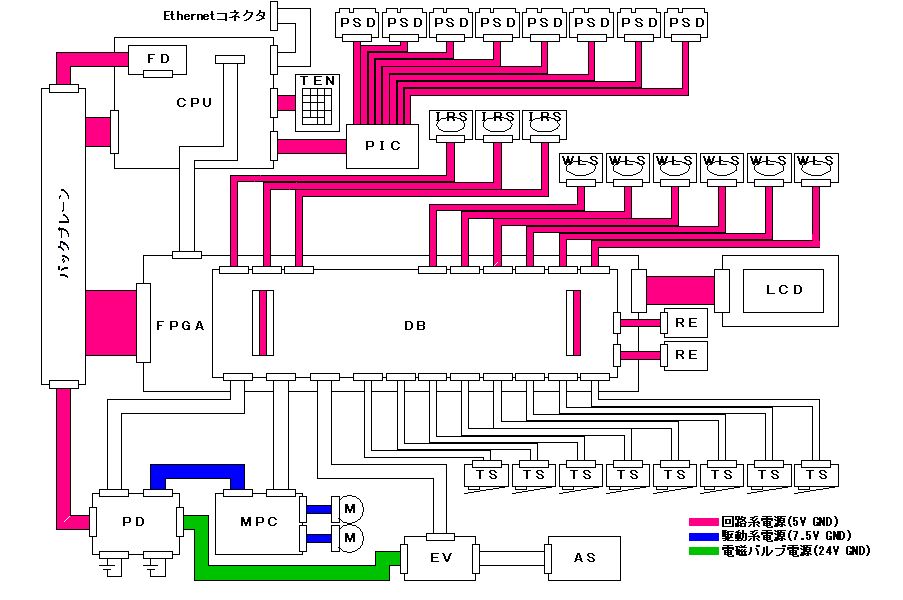

電源系統図

Fig3_2に電源系統図を示す。

4.機能性能

- 標準MIRS基板

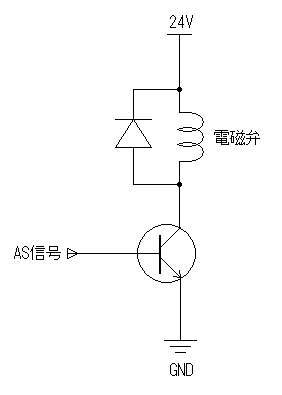

- 電磁弁制御ボード

- IO制御ボード

- FPGAボード

- CPUからFPGA回路情報をダウンロードできること。

- CPUからタッチセンサ(6)、赤外線センサ(3)の状態を読みこめること。

- ポストからの赤外線信号を区別でき、ポスト番号をCPUに出力出来ること。(ポスト番号は0から最大4まで)

- CPUより送られてくる液晶ディスプレイボード制御信号の出力制御を行う。

- CPUから送られてくる方向データをPWM変換して、MPCへ出力する。

- ロータリーエンコーダの回転数をカウントし、方向データと共に出力する。

- パワーオン信号の状態を読み込める。

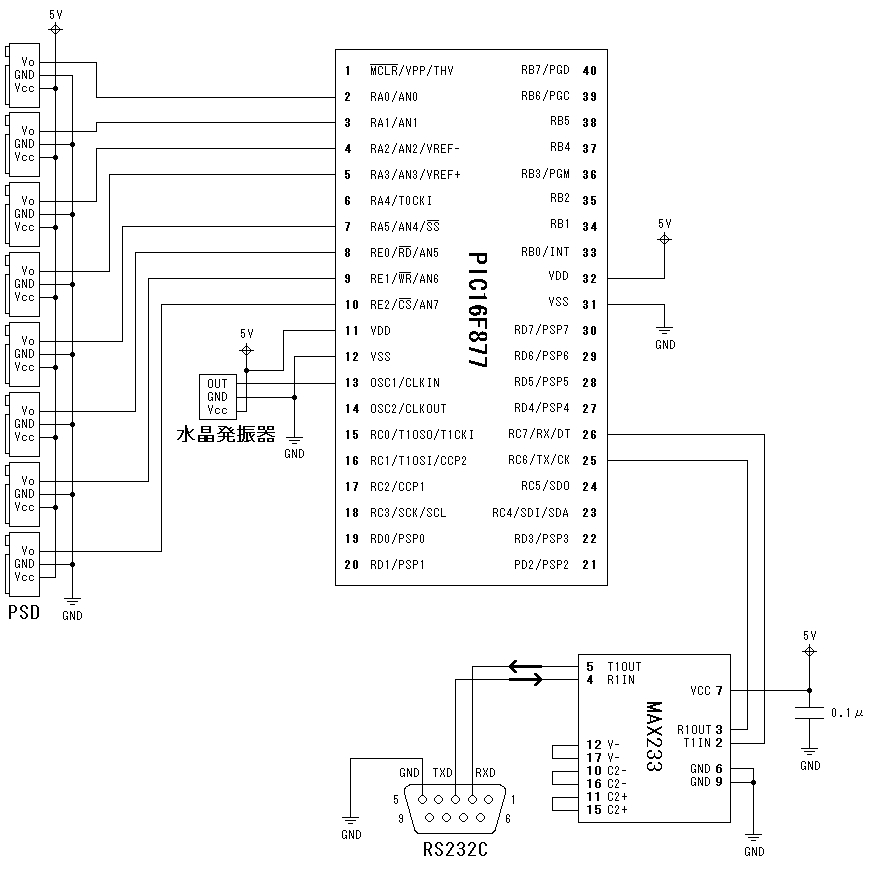

- PICボード

- PSDから送られでくる信号をA/D変換し、そのデータをCPUに送る。

- PSDはシャープGP2D12をつかう。この素子はブラックボックスで使え、5Vを掛けると、測定距離に応じた電圧を出力する。

- PIC16F877はアナログ入力が可能なピンが8つある。そのピンとPSDの出力ピンを1対1で対応させる。

- 水晶発振器は10MHzを発振する。

- MAX233はシリアル通信をするための、レベル変換用ICである。

- シリアルコネクタは9ピンDSUBコネクタをつかう。

PIC回路を以下に示す。

Fig.4_3 PIC回路

以下の基板、ボードについては標準MIRS基板を使用する。標準MIRS基板の仕様についてはMIRSデータベース(DBMD,ATML)参照。

新たに作成する電磁弁制御ボードの回路図を以下に示す。

IO制御ボードはISAバスを経由してCPUからセンサおよび回路の制御を行う機能を具備する。MIRS0205ではIO制御ボードをFPGA内に構成した回路データとドータボード,PICで構成する。

5.物理インターフェイス

-

ISAラック

ISAラックのインターフェースはISAバス規格に準拠し、各基板を下表に示すようにバックプレーンに搭載する。 Table.5_1_1 ISAラックへの基板の搭載方法 スロット.No ボード名称 備考 1 CPUボード 2 - 未使用 3 - 未使用 4 FPGAボード * スロットナンバーについてはバックプレーンの外観を参照。

-

バックプレーン - フラッシュディスク

- コネクタ名称 : BP_CN1

Fig.5_2_1 BP_CN1のコネクタ形状(bp_cn.jpg) Table.5_2_1 BP_CN1のインターフェース ピン.No 信号名 I/O 備考 1 Vcc - +5V 2 -5V - 未使用 3 -12V - 未使用 4 +12V - 未使用 5 GND - GND - 接続

フラッシュディスクから出ている電源接続用ケーブルをコネクタ付近で切断し、赤、黒それぞれのケーブルの先端に電源用ターミナルを圧着する。

次に赤ケーブルの電源用ターミナルをBP_CN1の1pinにねじとワッシャを用いて取りつけ、同様に黒ケーブルの電源用ターミナルをBP_CN1の5pinに取りつける。

- コネクタ名称 : BP_CN1

-

バックプレーン - 電源ボード

- コネクタ名称 : BP_CN1

Fig.5_3_1 BP_CN1のコネクタ形状(bp_cn.jpg) Table.5_3_1 BP_CN1のインターフェース ピン.No 信号名 I/O 備考 1 Vcc - +5V 2 -5V - 未使用 3 -12V - 未使用 4 +12V - 未使用 5 GND - GND - コネクタ名称 : PD_CN3 (MOLEX 53259-0220)

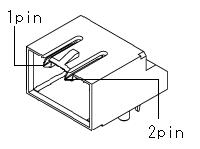

Fig.5_3_2 PD_CN3のコネクタ形状(53259-0220.jpg) Table.5_3_2 PD_CN3のインターフェース ピン.No 信号名 I/O 備考 1 Vcc - +5V 2 GND - GND - 接続

電源ケーブルの片側は電源用ターミナルを圧着してからBP_CN1にねじとワッシャを用いて取りつけ、

もう片側はMOLEX 51067用ターミナルを圧着してからMOLEX 51067-0220ハウジングに挿入し、PD_CN3に挿入する。

接続時のピン対応は下表を参照。また、+5Vには赤、GNDには黒の電源ケーブルを使用すること。Table.5_3_3 BP_CN1とPD_CN3のピン対応 BP_CN1 PD_CN3 ピン.No 信号名 ピン.No 信号名 1 Vcc <-> 1 Vcc 2 -5V <-> 3 -12V <-> 4 +12V <-> 5 GND <-> 2 GND

- コネクタ名称 : BP_CN1

-

CPUボード - パーソナルコンピュータ

- 接続

CPUボードの CPU_UTP にイーサネットケーブルを接続する。

- 接続

-

CPUボード−フラッシュディスク

- 接続

フラッシュディスクをCPUボードの CPU_IDE に挿入する。

- 接続

-

CPUボード - テンキー

- コネクタ名称 : CPU_KB/MOUSE(PS/2 コネクタメス)

- コネクタ名称 : PS/2 コネクタオス

- 接続

テンキーのケーブルコネクタをCPUボードのキーボードコネクタに接 続する。

-

CPUボード - PIC

- コネクタ名称 : RS232C(9ピンDSUBコネクタ)

- 接続

PICボードのケーブルコネクタをCPUボードのコネクタにつなぐ。

CPUボード - FPGAボード

- 接続

パラレルケーブルとパラレルケーブル用フラットケーブルを接続し、パラレルケーブルをFPGAボード、フラットケーブルをCPUボードに接続する。

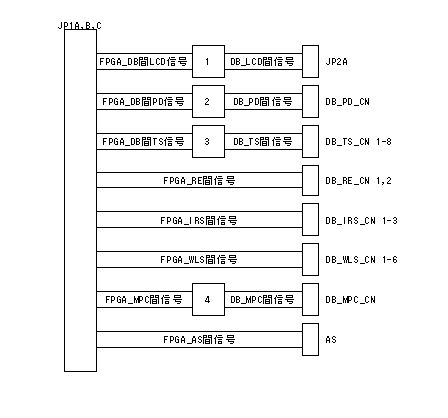

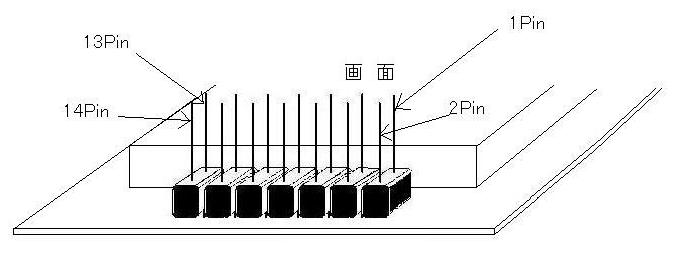

FPGAボード−LCD

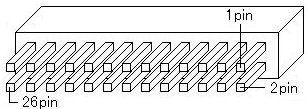

- コネクタ名称 : FPGA_CN4 (26pin ピンヘッダ型コネクタオス)

Fig.5_9_1 LCD_CNのコネクタ形状(26pin.jpg) Table.5_9_1 FPGA_CN4のインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 Vcc - +5V 14 LCD_DB7 INOUT データビット7 2 GND - GND 15 - - 未使用 3 Vee - コントラストADJ 16 - - 4 LCD_RS OUT レジスタセレクト 17 - - 5 LCD_R/W OUT READ/WRITE 18 - - 6 LCD_E OUT Enable信号 19 - - 7 LCD_DB0 INOUT データビット0 20 - - 8 LCD_DB1 INOUT データビット1 21 - - 9 LCD_DB2 INOUT データビット2 22 - - 10 LCD_DB3 INOUT データビット3 23 - - 11 LCD_DB4 INOUT データビット4 24 - - 12 LCD_DB5 INOUT データビット5 25 - - 13 LCD_DB6 INOUT データビット6 26 - - - コネクタ名称 : LCD_CN (26pin ピンヘッダ型コネクタオス)

Fig.5_9_2 LCD_CNのコネクタ形状(lcd_fpga.jpg) Table.5_9_2 LCD_CNのインターフェース ピン.No 信号名 I/O 備考 1 Vcc - +5V 2 GND - GND 3 Vee - コントラストADJ 4 RS LCD_IN レジスタセレクト 5 LCD_R/W IN READ/WRITE 6 LCD_E IN Enable信号 7 LCD_DB0 INOUT データビット0 8 LCD_DB1 INOUT データビット1 9 LCD_DB2 INOUT データビット2 10 LCD_DB3 INOUT データビット3 11 LCD_DB4 INOUT データビット4 12 LCD_DB5 INOUT データビット5 13 LCD_DB6 INOUT データビット6 14 LCD_DB7 INOUT データビット7 - 接続

26芯フラットケーブルの片側に26pin ピンヘッダ型コネクタ(メス)を圧着しFPGA_CN4に挿入する。

もう片側はケーブルを切断して14芯に変えてから14pin ピンヘッダ型コネクタ(メス)を圧着しLCD_FPGAに挿入する。

接続時のピン対応は下表を参照。Table.5_9_3 FPGA_CN4 と LCD_CNのピン対応 FPGA_CN4 LCD_CN FPGA_CN4 LCD_CN ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 1 Vcc <-> 1 Vcc 14 LCD_DB7 <-> 14 LCD_DB7 2 GND <-> 2 GND 15 - <-> 3 Vee <-> 3 Vee 16 - <-> 4 LCD_RS <-> 4 LCD_RS 17 - <-> 5 LCD_R/W <-> 5 LCD_R/W 18 - <-> 6 LCD_E <-> 6 LCD_E 19 - <-> 7 LCD_DB0 <-> 7 LCD_DB0 20 - <-> 8 LCD_DB1 <-> 8 LCD_DB1 21 - <-> 9 LCD_DB2 <-> 9 LCD_DB2 22 - <-> 10 LCD_DB3 <-> 10 LCD_DB3 23 - <-> 11 LCD_DB4 <-> 11 LCD_DB4 24 - <-> 12 LCD_DB5 <-> 12 LCD_DB5 25 - <-> 13 LCD_DB6 <-> 13 LCD_DB6 26 - <->

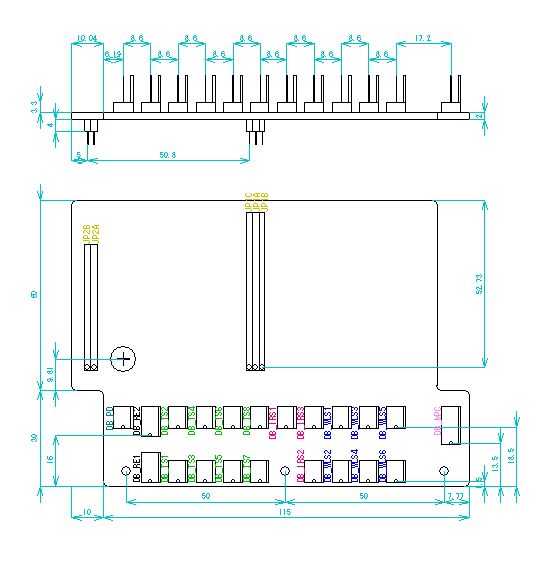

FPGAボード−ドータボード

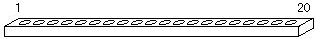

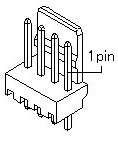

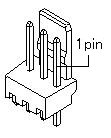

- コネクタ名称 : FPGA_JP20A (20pin ジャンパコネクタメス)

Fig.5_10_1 FPGA_JP20Aのコネクタ形状(jp20.jpg)

* コネクタの取りつけ位置、および方向はマイコンビルダー取扱説明書を参照。Table.5_10_1 FPGA_JP20Aのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1(F1-144) TS1 IN タッチセンサ信号1 11(F1-162) R2B IN ロータリーエンコーダ2 chB 2(F1-147) TS2 IN タッチセンサ信号2 12(F1-163) R2A IN ロータリーエンコーダ2 chA 3(F1-148) TS3 IN タッチセンサ信号3 13(F1-164) R_DIR OUT MPC 右方向信号。オープンコレクタ出力 4(F1-149) TS4 IN タッチセンサ信号4 14(F1-166) R_PWM OUT MPC 右PWM信号。オープンコレクタ出力 5(F1-150) TS5 IN タッチセンサ信号5 15(F1-167) L_DIR OUT MPC 左方向信号。オープンコレクタ出力 6(F1-157) TS6 IN タッチセンサ信号6 16(F1-168) L_PWM OUT MPC 左PWM信号。オープンコレクタ出力 7(F1-158) TS7 IN タッチセンサ信号7 17(F1-169) 未使用 8(F1-159) TS8 IN タッチセンサ信号8 18(F1-170) 未使用 9(F1-160) R1B IN ロータリーエンコーダ1 chB 19(F1-172) 未使用 10(F1-161) R1A IN ロータリーエンコーダ1 chA 20(F1-173) 未使用 - コネクタ名称 : DB_JP1A (20pin ジャンパコネクタオス)

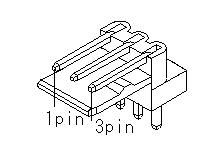

Fig.5_10_2 DB_JP1Aのコネクタ形状( db_j20.jpg)

* コネクタの取りつけ位置、および方向はドーターボード外形図を参照。Table.5_10_2 DB_JP1Aのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1(F1-144) TS1 OUT タッチセンサ信号1 11(F1-162) R2B OUT ロータリーエンコーダ2 chB 2(F1-147) TS2 OUT タッチセンサ信号2 12(F1-163) R2A OUT ロータリーエンコーダ2 chA 3(F1-148) TS3 OUT タッチセンサ信号3 13(F1-164) R_DIR IN MPC 右方向信号。オープンコレクタ出力 4(F1-149) TS4 OUT タッチセンサ信号4 14(F1-166) R_PWM IN MPC PWM信号。オープンコレクタ出力 5(F1-150) TS5 OUT タッチセンサ信号5 15(F1-167) L_DIR IN MPC 左方向信号。オープンコレクタ出力 6(F1-157) TS6 OUT タッチセンサ信号6 16(F1-168) L_PWM IN MPC 左PWM信号。オープンコレクタ出力 7(F1-158) TS7 OUT タッチセンサ信号7 17(F1-169) 未使用 8(F1-159) TS8 OUT タッチセンサ信号8 18(F1-170) 未使用 9(F1-160) R1B OUT ロータリーエンコーダ1 chB 19(F1-172) 未使用 10(F1-161) R1A OUT ロータリーエンコーダ1 chA 20(F1-173) 未使用 - コネクタ名称 : FPGA_JP30C (20pin ジャンパコネクタメス)

Fig.5_10_3 FPGA_JP30Cのコネクタ形状(jp20.jpg)

* コネクタの取りつけ位置、および方向はマイコンビルダー取扱説明書を参照。Table.5_10_3 FPGA_JP30Cのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1(F1-204) WLS1 IN 白線センサ1 11 未使用 2(F1-203) WLS2 IN 白線センサ2 12 未使用 3(F1-202) WLS3 IN 白線センサ3 13 未使用 4(F1-201) WLS4 IN 白線センサ4 14 未使用 5(F1-200) WLS5 IN 白線センサ5 15 Vcc - 5V 6(F1-199) WLS6 IN 白線センサ6 16 Vcc - 5V 7 未使用 17 Vcc - 5V 8 未使用 18 Vcc - 5V 9 未使用 19 Vcc - 5V 10 未使用 20 Vcc - 5V - コネクタ名称 : DB_JP1B (20pin ジャンパコネクタオス)

Fig.5_10_4 DB_JP1Bのコネクタ形状(db_j20.jpg)

* コネクタの取りつけ位置、および方向はドーターボード外形図を参照。Table.5_10_4 DB_JP1Bのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1(F1-205) WLS1 OUT 白線センサ1 11 未使用 2(F1-204) WLS2 OUT 白線センサ2 12 未使用 3(F1-203) WLS3 OUT 白線センサ3 13 未使用 4(F1-202) WLS4 OUT 白線センサ4 14 未使用 5(F1-201) WLS5 OUT 白線センサ5 15 Vcc - 5V 6(F1-200) WLS6 OUT 白線センサ6 16 Vcc - 5V 7 未使用 17 Vcc - 5V 8 未使用 18 Vcc - 5V 9 未使用 19 Vcc - 5V 10 未使用 20 Vcc - 5V - コネクタ名称 : FPGA_JP20B (20pin ジャンパコネクタメス)

Fig.5_10_5 FPGA_JP20Bのコネクタ形状(jp20.jpg)

* コネクタの取りつけ位置、および方向はマイコンビルダー取扱説明書を参照。Table.5_10_5 FPGA_JP20Bのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1(F1-204) IRS1 IN 赤外線センサ1 11(F1-192) LCD_R/W OUT LCD リード・ライト 2(F1-203) IRS2 IN 赤外線センサ2 12(F1-191) LCD_E OUT LCD イネーブル 3(F1-202) IRS3 IN 赤外線センサ3 13(F1-190) LCD_DB0 INOUT LCD データ 0 4 未使用 14(F1-189) LCD_DB1 INOUT LCD データ 1 5 未使用 15(F1-187) LCD_DB2 INOUT LCD データ 2 6 未使用 16(F1-179) LCD_DB3 INOUT LCD データ 3 7 未使用 17(F1-177) LCD_DB4 INOUT LCD データ 4 8 未使用 18(F1-176) LCD_DB5 INOUT LCD データ 5 9(F1-195) PO IN パワーオン信号 19(F1-175) LCD_DB6 INOUT LCD データ 6 10(F1-193) LCD_RS OUT LCD レジスタセレクト 20(F1-174) LCD_DB7 INOUT LCD データ 7 - コネクタ名称 : DB_JP1C (20pin ジャンパコネクタオス)

Fig.5_10_6 DB_JP1Cのコネクタ形状( db_j20.jpg)

* コネクタの取りつけ位置、および方向はドーターボード外形図を参照。Table.5_10_6 DB_JP1Cのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1(F1-204) IRS1 OUT 赤外線センサ1 11(F1-192) LCD_R/W IN LCD リード・ライト 2(F1-203) IRS2 OUT 赤外線センサ2 12(F1-191) LCD_E IN LCD イネーブル 3(F1-202) IRS3 OUT 赤外線センサ3 13(F1-190) LCD_DB0 INOUT LCD データ 0 4 未使用 14(F1-189) LCD_DB1 INOUT LCD データ 1 5 未使用 15(F1-187) LCD_DB2 INOUT LCD データ 2 6 未使用 16(F1-179) LCD_DB3 INOUT LCD データ 3 7 未使用 17(F1-177) LCD_DB4 INOUT LCD データ 4 8 未使用 18(F1-176) LCD_DB5 INOUT LCD データ 5 9(F1-195) PO OUT パワーオン信号 19(F1-175) LCD_DB6 INOUT LCD データ 6 10(F1-193) LCD_RS IN LCD レジスタセレクト 20(F1-174) LCD_DB7 INOUT LCD データ 7 - コネクタ名称 : FPGA_JP60B (26pin ジャンパコネクタメス)

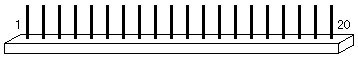

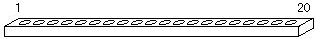

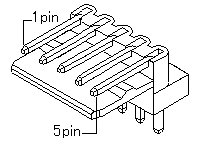

Fig.5_10_7 FPGA_JP60Bのコネクタ形状(jp26.jpg)

* コネクタの取りつけ位置、および方向はマイコンビルダー取扱説明書を参照。Table.5_10_7 FPGA_JP60Bのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 Vcc - 5V 8 LCD_DB1 INOUT LCD データ 1 2 GND - GND 9 LCD_DB2 INOUT LCD データ 2 3 Vo - LCD コントラストアドジャスト 10 LCD_DB3 INOUT LCD データ 3 4 LCD_RS IN LCD レジスタセレクト 11 LCD_DB4 INOUT LCD データ 4 5 LCD_R/W IN LCD リード・ライト 12 LCD_DB5 INOUT LCD データ 5 6 LCD_E IN LCD イネーブル 13 LCD_DB6 INOUT LCD データ 6 7 LCD_DB0 INOUT LCD データ 0 14 LCD_DB7 INOUT LCD データ 7 - コネクタ名称 : DB_JP2A (14pin ジャンパコネクタオス)

Fig.5_10_8 DB_JP2Aのコネクタ形状(db_j14.jpg)

* コネクタの取りつけ位置、および方向はドーターボード外形図を参照。Table.5_10_8 DB_JP2Aのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 Vcc - 5V 8 LCD_DB1 INOUT LCD データ 1 2 GND - GND 9 LCD_DB2 INOUT LCD データ 2 3 Vo - LCD コントラストアドジャスト 10 LCD_DB3 INOUT LCD データ 3 4 LCD_RS OUT LCD レジスタセレクト 11 LCD_DB4 INOUT LCD データ 4 5 LCD_R/W OUT LCD リード・ライト 12 LCD_DB5 INOUT LCD データ 5 6 LCD_E OUT LCD イネーブル 13 LCD_DB6 INOUT LCD データ 6 7 LCD_DB0 INOUT LCD データ 0 14 LCD_DB7 INOUT LCD データ 7 - コネクタ名称 : FPGA_JP60C (26pin ジャンパコネクタメス)

Fig.5_10_9 FPGA_JP60Cのコネクタ形状(jp26.jpg)

* コネクタの取りつけ位置、および方向はマイコンビルダー取扱説明書を参照。Table.5_10_9 FPGA_JP60Cのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 GND - GND 8 GND - GND 2 GND - GND 9 GND - GND 3 GND - GND 10 GND - GND 4 GND - GND 11 GND - GND 5 GND - GND 12 GND - GND 6 GND - GND 13 GND - GND 7 GND - GND 14 GND - GND - コネクタ名称 : DB_JP2B (14pin ジャンパコネクタオス)

Fig.5_10_10 DB_JP2Bのコネクタ形状(db_j14.jpg)

* コネクタの取りつけ位置、および方向はドーターボード外形図を参照。Table.5_10_10 DB_JP2Bのインターフェース ピン.No 信号名 I/O 備考 ピン.No 信号名 I/O 備考 1 GND - GND 8 GND - GND 2 GND - GND 9 GND - GND 3 GND - GND 10 GND - GND 4 GND - GND 11 GND - GND 5 GND - GND 12 GND - GND 6 GND - GND 13 GND - GND 7 GND - GND 14 GND - GND - 接続

ドーターボードはFPGAボードの亀の子基盤となっているので、各ボードのコネクタが下表の対応関係になるようにドーターボードをFPGAボードに挿しこむ。 Table.5_10_11 FPGAボードコネクタとドーターボードコネクタの対応関係 FPGAボード ドーターボード JP20A <-> JP1A JP30C <-> JP1B JP20B <-> JP1C JP60B(1pin to 14pin) <-> JP2A JP60C(1pin to 14pin) <-> JP2B

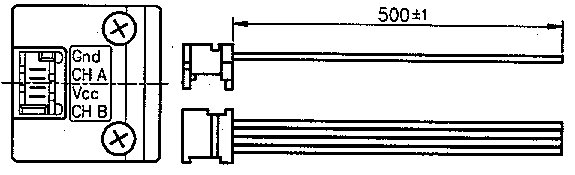

ドータボード−ロータリエンコーダ

- コネクタ名称 : DB_RE1、DB_RE2(MOLEX 5045-04A)

Fig.5_11_1 DB_RE1、DB_RE2のコネクタ形状(5045a-04.jpeg) Table.5_11_1 DB_RE1,DB_RE2のインターフェース ピン.No 信号名 I/O 備考 1 CH_A IN チャネルB層の信号 2 CH_B IN チャンネルB層の信号 3 Vcc - +5V 4 GND - GND - コネクタ名称 : RE1_CN,RE2_CN (ロータリエンコーダコネクタ)

Fig.5_11_2 RE1_CN,RE2_CNのコネクタ形状とコネクタケーブル形状(reconect.jpeg) Table.5_11_2 RE1_CN,RE2_CNのインターフェイス ピン.No 信号名 I/O 備考 1 CH_B OUT チャネルB層の信号 2 Vcc - +5V 3 CH_A OUT チャネルA層の信号 4 GND - GND - 接続

4芯フラットケーブルの両端を1本ずつ裂き、片側はそれぞれにMOLEX 5051用ターミナルを圧着してからMOLEX 5051-5ハウジングに挿入し、それぞれDB_REN に挿入する。

もう片側はロータリエンコーダ付属ケーブルと接続し、接続部の絶縁処理を行う。 接続時のピン対応は下表を参照。Table.5_11_3 DB_RE1,DB_RE2 と RE1_CN,RE2_CN のピン対応 DB_RE1 RE1_DB ピン.No 信号名 ピン.No 信号名 1 CH_B <-> 1 CH_B 2 Vcc <-> 2 Vcc 3 CH_A <-> 3 CH_B 4 GND <-> 4 GND DB_RE2 RE2_DB ピン.No 信号名 ピン.No 信号名 1 CH_B <-> 1 CH_B 2 Vcc <-> 2 Vcc 3 CH_A <-> 3 CH_B 4 GND <-> 4 GND

ドータボード−タッチセンサ

- コネクタ名称 : DB_TSN (N =1 to 8) (MOLEX 5045-03A)

Fig.5_12_1 DB_TSN のコネクタ形状(5045a-03.jpg) Table.5_12_1 DB_TSN のインターフェース ピン.No 信号名 I/O 備考 1 GND - GND 2 TSON IN タッチセンサON信号 3 TSOF IN タッチセンサOFF信号 - コネクタ名称 : Micro Switch N (N =1 to 8)(omronSS-5GL)

Fig.5_12_2 Micro Switch N のコネクタ形状(ts.jpg) Table.5_12_2 Micro Switch N のインターフェース ピン.No 信号名 I/O 備考 1 GND - GND 2 TSON OUT タッチセンサON信号 3 TSOF OUT タッチセンサOFF信号 - 接続

3芯のフラットケーブルの両端を1本ずつ裂いてから片側に5051用ターミナルを圧着してMOLEX 5051ハウジングに挿入し、DB_TSN に挿入する。もう片側は絶縁ビニルを剥いてからマイクロスイッチにはんだ付けする。

接続時のピン対応は下表を参照。Table.5_12_3 DB_TSN と Micro Switch N のピン対応 DB_TS1 Micro Switch 1 DB_TS5 Micro Switch 5 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 1 GND <-> 1 GND 1 GND <-> 1 GND 2 TSON <-> 2 TSON 2 TSON <-> 2 TSON 3 TSOF <-> 3 TSOF 3 TSOF <-> 3 TSOF DB_TS2 Micro Switch 2 DB_TS6 Micro Switch 6 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 1 GND <-> 1 GND 1 GND <-> 1 GND 2 TSON <-> 2 TSON 2 TSON <-> 2 TSON 3 TSOF <-> 3 TSOF 3 TSOF <-> 3 TSOF DB_TS3 Micro Switch 3 DB_TS7 Micro Switch 7 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 1 GND <-> 1 GND 1 GND <-> 1 GND 2 TSON <-> 2 TSON 2 TSON <-> 2 TSON 3 TSOF <-> 3 TSOF 3 TSOF <-> 3 TSOF DB_TS4 Micro Switch 4 DB_TS8 Micro Switch 8 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 1 GND <-> 1 GND 1 GND <-> 1 GND 2 TSON <-> 2 TSON 2 TSON <-> 2 TSON 3 TSOF <-> 3 TSOF 3 TSOF <-> 3 TSOF

ドータボード−赤外線センサ

- コネクタ名称 : DB_IRSN (N =1 to 8) (MOLEX 5045-03A)

Fig.5_13_1 DB_IRSN のコネクタ形状(5045a-03.jpg) Table.5_13_1 DB_IRSN のインターフェース ピン.No 信号名 I/O 備考 1 GND - GND 2 Vcc - Vcc 3 Vo IN 赤外線受光信号 - コネクタ名称 : IRSN_CN (N =1 to 8) (MOLEX 5045-03A)

Fig.5_13_2 IRSN_CNのコネクタ形状(5045a-03.jpg) Table.5_13_2 IRSN_CNのインターフェース ピン.No 信号名 I/O 備考 1 Vo OUT 赤外線受光信号 2 GND - GND 3 Vcc - +5V - 接続

3芯のフラットケーブルの両端を1本ずつ裂いてからそれぞれに5051用ターミナルを圧着してMOLEX 5051ハウジングに挿入する。

それからそれぞれをDB_IRSN とIRSN_DBに挿入する。接続時のピン対応は下表を参照。Table.5_13_3 DB_IRSN と IRSN_CN のピン対応 DB_IRS0 IRS0_CN DB_IRS4 IRS4_CN ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 3 Vo <-> 1 Vo 3 Vo <-> 1 Vo 1 GND <-> 2 GND 1 GND <-> 2 GND 2 Vcc <-> 3 Vcc 2 Vcc <-> 3 Vcc DB_IRS1 IRS1_CN DB_IRS5 IRS5_CN ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 3 Vo <-> 1 Vo 3 Vo <-> 1 Vo 1 GND <-> 2 GND 1 GND <-> 2 GND 2 Vcc <-> 3 Vcc 2 Vcc <-> 3 Vcc DB_IRS2 IRS2_CN DB_IRS6 IRS6_CN ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 3 Vo <-> 1 Vo 3 Vo <-> 1 Vo 1 GND <-> 2 GND 1 GND <-> 2 GND 2 Vcc <-> 3 Vcc 2 Vcc <-> 3 Vcc DB_IRS3 IRS3_CN DB_IRS7 IRS7_CN ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 3 Vo <-> 1 Vo 3 Vo <-> 1 Vo 1 GND <-> 2 GND 1br> GND <-> 2 GND 2 Vcc <-> 3 Vcc 2 Vcc <-> 3 Vcc

ドータボード−白線センサ

- コネクタ名称 : DB_LS n (n =1 to 4) (MOLEX 5045-03A)

Fig.5_14_1 DB_LS n のコネクタ形状

Table.5_14_1 DB_LS n のインターフェース

ピン.No 信号名 I/O 備考 1 Vo IN 白線感知信号 2 GND - GND 3 Vcc - +5V - コネクタ名称 : LS_CN n (n =1 to 4) (MOLEX 5045-03A)

Fig.5_14_2 LS_CN nのコネクタ形状

Table.5_14_2 LS_CN nのインターフェース

ピン.No 信号名 I/O 備考 1 Vo OUT 白線感知信号 2 GND - GND 3 Vcc - +5V - 接続

3芯のフラットケーブルの両端を1本ずつ裂いてからそれぞれに5051用ターミナルを圧着してMOLEX 5051ハウジングに挿入する。

それからそれぞれをDB_LS n とLS_CN nに挿入する。接続時のピン対応は下表を参照。Table.5_14_3 DB_LS n と LS_CN nのピン対応 DB_LS 1 LS_CN 1 DB_LS 3 LS_CN 3 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 1 Vo <-> 1 Vo 1 Vo <-> 1 Vo 2 GND <-> 2 GND 2 GND <-> 2 GND 3 Vcc <-> 3 Vcc 3 Vcc <-> 3 Vcc DB_LS 2 LS_CN 2 DB_LS 4 LS_CN 4 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 ピン.No 信号名 1 Vo <-> 1 Vo 1 Vo <-> 1 Vo 2 GND <-> 2 GND 2 GND <-> 2 GND 3 Vcc <-> 3 Vcc 3 Vcc <-> 3 Vcc

ドータボード−モーターパワー制御ボード

- コネクタ名称 : DB_MPC (MOLEX 5045-05A)

Fig.5_15_1 DB_MPCのコネクタ形状(5045a-05.jpg) Table.5_15_1 DB_MPCのインターフェース ピン.No 信号名 I/O 備考 1 Vcc - +5V 2 L_OUT1 OUT 左PWM信号 3 R_OUT1 OUT 右方向信号 4 L_OUT2 OUT 左方向信号 5 R_OUT2 OUT 右PWM信号 - コネクタ名称 : MPC_CN1 (MOLEX 5046-05A)

Fig.5_15_2 MPC_CN1のコネクタ形状(5046a.jpg) Table.5_15_2 MPC_CN1のインターフェース ピン.No 信号名 I/O 備考 1 L_OUT1 IN 左PWM信号 2 R_OUT1 IN 右方向信号 3 R_OUT2 IN 右PWM信号 4 L_OUT2 IN 左方向信号 5 Vcc - +5V - 接続

5芯フラットケーブルを用意し、両端をそれぞれ1本ずつにわける。次に両側の絶縁ビニルを剥き、MOLEX 53259用ターミナルを圧着してからMOLEX 53259-0220ハウジングに挿入し、それぞれをDB_MPCとMPC_DB に挿入する。

接続時のピン対応は下表を参照。Table.5_15_3 DB_MPC と MPC_CN1 のピン対応 DB_MPC MPC_CN1 ピン.No 信号名 ピン.No 信号名 1 Vcc <-> 5 Vcc 2 L_OUT1 <-> 1 L_OUT1 3 R_OUT1 <-> 2 R_OUT1 4 L_OUT2 <-> 4 L_OUT2 5 R_OUT2 <-> 3 R_OUT2

ドータボード−電源ボード

- コネクタ名称 : DB_PD (MOLEX 5045-03A)

Fig.5_16_1 DB_PDのコネクタ形状(5045a-03.jpg) Table.5_16_1 DB_PDのインターフェース ピン.No 信号名 I/O 備考 1 - - 未使用 2 Vsig - 駆動系電源ON信号 3 GND - GND - コネクタ名称 : PD_CN5 (MOLEX 5046-03A)

Fig.5_16_2 PD_CN5のコネクタ形状(5046-3m.jpg) Table.5_16_2 PD_CN5のインターフェース ピン.No 信号名 I/O 備考 1 - - 未使用 2 Vsig - 駆動系電源ON信号 3 GND - GND - 接続

3芯のフラットケーブルの両端を1本ずつ裂いてからそれぞれに5051用ターミナルを圧着してMOLEX 5051ハウジングに挿入する。

それからそれぞれをDB_PDとPD_DBに挿入する。接続時のピン対応は下表を参照。Table.5_16_3 DB_PD と PD_CN5 のピン対応 DB_PD PD_CN5 ピン.No 信号名 ピン.No 信号名 1 - <-> 1 - 2 Vsig <-> 2 Vsig 3 GND <-> 3 GND

電源ボード−モーターパワー制御ボード

- コネクタ名称 : MPC_CN2 (MOLEX 53259-0220)

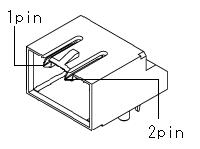

Fig.5_17_1 MPC_CN2のコネクタ形状(53259-0220.jpg) Table.5_17_1 MPC_CN2のインターフェース ピン.No 信号名 I/O 備考 1 Vin - +7.2V 2 GND - GND - コネクタ名称 : PD-CN4 (MOLEX 53259-0220)

Fig.5_17_2 PD_CN4のコネクタ形状(53259-0220.jpg) Table.5_17_2 PD_CN4のインターフェース ピン.No 信号名 I/O 備考 1 Vin - +7.2V 2 GND - GND - 接続

電源ケーブルの両端にMOLEX 51067用ターミナルを圧着してからMOLEX 51067-0220ハウジングに挿入し、MPC_PDとPD_MPCに挿入する。

接続時のピン対応は下表を参照。また、Vinには赤、GNDには黒の電源ケーブルを使用すること。Table.5_17_3 MPC_CN2 と PD_CN4 のピン対応 MPC_PD PD_MPC ピン.No 信号名 ピン.No 信号名 1 Vin <-> 1 Vin 2 GND <-> 2 GND

電源ボード−バッテリー

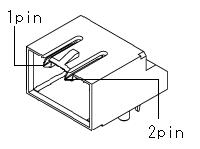

- コネクタ名称 : PD_CN1,PD_CN2 (MOLEX 53259-0220)

Fig.5_18_1 PD_CN1,PD_CN2のコネクタ形状(53259-0220.jpg) Table.5_18_1 PD_CN1,PD_CN2のインターフェース ピン.No 信号名 I/O 備考 1 Vin - +7.2 2 GND - GND - コネクタ名称 : バッテリコネクタ 1,2

Fig.5_18_2 バッテリコネクタ 1,2のコネクタ形状(battery.jpg) Table.5_18_2 バッテリコネクタ 1,2のインターフェース ピン.No 信号名 I/O 備考 1 Vin - +7.2V 2 GND - GND - 接続

電源ケーブルの片側は、バッテリコネクタのターミナルを圧着してバッテリコネクタハウジングに入れる。

もう片側はMOLEX 51067用ターミナルを圧着してからMOLEX 51067-0220ハウジングに挿入し、PD_M.PD_VCCに挿入する。

接続時のピン対応は下表を参照。また、Vinには赤、GNDには黒の電源ケーブルを使用すること。Table.5_18_3 PD_CN1,PD_CN2 とバッテリコネクタ 1,2のピン対応 PD_M バッテリコネクタ 1 ピン.No 信号名 ピン.No 信号名 1 Vin <-> 1 Vin 2 GND <-> 2 GND PD_VCC バッテリコネクタ 2 ピン.No 信号名 ピン.No 信号名 1 Vin <-> 1 Vin 2 GND <-> 2 GND

モーターパワー制御ボード−モーター

- コネクタ名称 : MPC_CN3,MPC_CN4 (MOLEX 53259-0220)

Fig.5_19_1 MPC_CN3,MPC_CN4のコネクタ形状(53259-0220.jpg) Table.5_19_1 MPC_CN3,MPC_CN4のインターフェース ピン.No 信号名 I/O 備考 1 Vo1 - 正極 2 Vo2 - 負極 - コネクタ名称 : M1,M2 (MAXONモータの端子)

Table.5_19_2 M1,M2のインターフェース

* モータの端子付近に"+"とかいてあるほうが正極。ピン.No 信号名 I/O 備考 1 Vo1 - 正極 2 Vo2 - 負極 - 接続

電源ケーブルの片側にMOLEX 53259用ターミナルを圧着してからMOLEX 53259-0220ハウジングに挿入し、MPC_CN3,MPC_CN4に挿入。

もう片方は絶縁ビニルを剥きモータの端子にはんだ付けする。

接続時のピン対応は下表を参照。また、正極には赤、負極には黒の電源ケーブルを使用すること。Table.5_19_3 MPC_CN3,MPC_CN4 と M1,2 のピン対応 MPC_CN3 M1 ピン.No 信号名 ピン.No 信号名 1 Vo1 <-> 1 Vo1 2 Vo2 <-> 2 Vo2 MPC_CN4 M2 ピン.No 信号名 ピン.No 信号名 1 Vo1 <-> 1 Vo1 2 Vo2 <-> 2 Vo2

- 接続

6.各部の詳細

-

標準MIRS基板

- CPUボード仕様(現在作成中)

- 可逆モータパワー変換ボード仕様

- 赤外線センサボード取り扱い説明書

- 電源ボード(PD)取り扱い説明書

MIRS0205が作成する基板、回路

IO制御ボードはFPGA内に構成した回路データとドータボード0205で構成される。-

FPGAボード内に構成する各モジュールの回路データ

- 各ブロックの機能

- 1. アドレスデコーダ

: 16bitのアドレスデータからモジュールセレクタ信号を作り出し、AEN信号に合わせて各モジュールに出力する。また、各モジュールが16bitのデータ入出力を行えるようにIOCS16 信号を制御する。 - 2. 液晶ディスプレイ制御モジュール

: CPUから送られてくる8bitの液晶ディスプレイボード制御信号の出力制御を行う。 - 3. モータパワー制御モジュール

: CPUから送られてくる速度データをPWM変換し、同じくCPUから送られてくる方向データと共に出力する。 - 4. タッチセンサ、パワーオン信号、EV制御信号処理モジュール

: 8bitのタッチセンサ信号、1bitのパワーオン信号を16bitのTP信号としてCPUに出力する。CPUから送られてくる1bitのEV制御信号の出力制御を行う。タッチセンサ信号、パワーオン信号に変化が生じた時、CPUから割り込みリセット信号が来るまでCPUに割り込み信号を出力する。 - 5. 赤外線センサ信号処理モジュール

: 赤外線センサにポストからの信号入力が入った時割り込み信号を出力し、要求があれば符号化された信号を12bitのパラレルデータとしてCPUに出力する。 - 6. ダミーモジュール

: ISAバスの信号の内、ATLMIRS用の各モジュールで使用しない信号をハイインピーダンスに接続する。 - 7. ロータリーエンコーダ制御モジュール

: ドーターボードを通して送られてくるロータリーエンコーダのデータを用いて、方向データ、カウント値を出力する。 - モジュール間インターフェース

- ISA バス

ISA バスのインターフェースについては ISA バスの仕様書、およびマイコンビルダーの仕様書を参照のこと。 - アドレスデコーダ

Table.6_1_2_1 アドレスデコーダのインターフェース 信号名 I/O 機能 SA 0 to 15 OUT 16bit アドレスバス IOCS16 OUT 16bit I/Oサイクルに 1 ウェイトで応答 LCD_ADD OUT LCD_Mセレクタ信号 MPC_ADD OUT MPC_Mセレクタ信号 USS_ADD OUT USS_Mセレクタ信号 RE_ADD OUT RE_Mセレクタ信号 TIP_ADD OUT TP_Mセレクタ信号 IRS_ADD,IRS_RS OUT IRS_Mセレクタ信号 - 液晶ディスプレイ制御モジュール

Table.6_1_2_2 液晶ディスプレイ制御モジュールのインターフェース 信号名 I/O 機能 IB_SD 0 to 15 OUT 16bit データバス B_IORN IN I/Oリード・ストローブ B_IOWN IN I/Oライト・ストローブ B_RESET IN システム・リセット B_CLK IN システム・クロック 8MHz デューティ50% LCD_RS OUT レジスタ・セレクト LCD_R/W OUT リード・ライト LCD_E OUT イネーブル信号 OB_DB 0 to 7 OUT 出力データ - モータパワー制御モジュール

Table.6_1_2_3 モータパワー制御モジュールのインターフェース 信号名 I/O 機能 IB_SD 0 to 15 IN 16bit データバス OB_SD 0 to 7 OUT 8bit データバス B_IORN IN I/Oリード・ストローブ B_IOWN IN I/Oライト・ストローブ B_RESET IN システム・リセット B_CLK IN システム・クロック 8MHz デューティ50% R_OUT1 OUT MPC_DATA。オープンコレクタ出力 R_OUT2 OUT MPC_DATA。オープンコレクタ出力 L_OUT1 OUT MPC_DATA。オープンコレクタ出力 L_OUT2 OUT MPC_DATA。オープンコレクタ出力 - ロータリーエンコーダ制御モジュール

Table.6_1_2_4 ロータリーエンコーダ制御モジュールのインターフェース 信号名 方 向 対 象 概 要 RE_X IN アドレスデコーダ モジュールセレクタ信号(Xカウンタ選択用) RE_Y IN アドレスデコーダ モジュールセレクタ信号(Yカウンタ選択用) SD 0 to 15 INOUT ISA-Bus 16bit データバス IOR IN ISA-Bus I/Oリード・ストローブ IOW IN ISA-Bus I/Oライト・ストローブ RESET IN ISA-Bus システム・リセット CLK IN ISA-Bus システム・クロック 8MHz デューティ50% X_A,X_B IN ドーターボード Xカウンタ用2相信号入力端子 Y_A,Y_B IN ドーターボード Yカウンタ用2相信号入力端子 - タッチセンサ、パワーボード信号、EV制御信号処理モジュール

Table.6_1_2_5 タッチセンサ、パワーボード信号、EV制御信号処理モジュールのインターフェース 信号名 I/O 機能 TP_DATA 0 to 15 OUT 16bit データバス B_IORN IN I/Oリード・ストローブ B_IOWN IN I/Oライト・ストローブ B_RESET IN システム・リセット B_CLK IN システム・クロック 8MHz デューティ50% PO IN パワーオン信号 EV IN EV制御信号 TS 0 to 7 IN タッチセンサ信号

- 赤外線センサ信号処理モジュール

Table.6_1_2_6 赤外線センサ信号処理モジュールのインターフェース 信号名 I/O 機能 IRS_DATA 0 to 15 OUT 16bit データバス OB_SD 0 OUT モジュールリセット B_IORN IN I/Oリード・ストローブ B_IOWN IN I/Oライト・ストローブ B_RESET IN システム・リセット B_CLK IN システム・クロック 8MHz デューティ50% IRS 0 to 7 IN 赤外線センサ信号 IRS_ADD IN 赤外線センサ選択信号 IRS_RS IN 赤外線センサリセット信号

- ISA バス

Fig.6_2_1 FPGA内回路ブロック図

- CPUボード仕様(現在作成中)