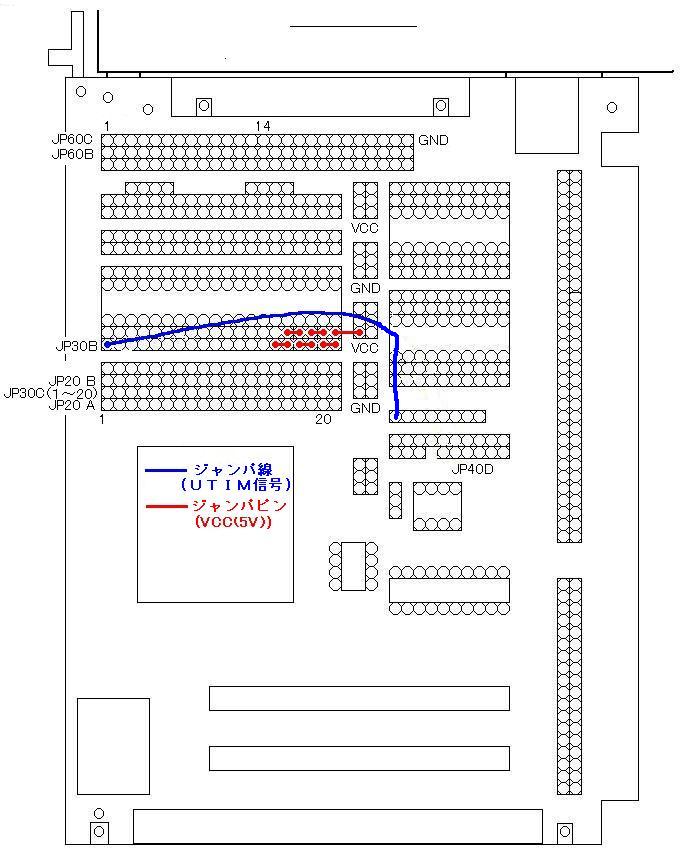

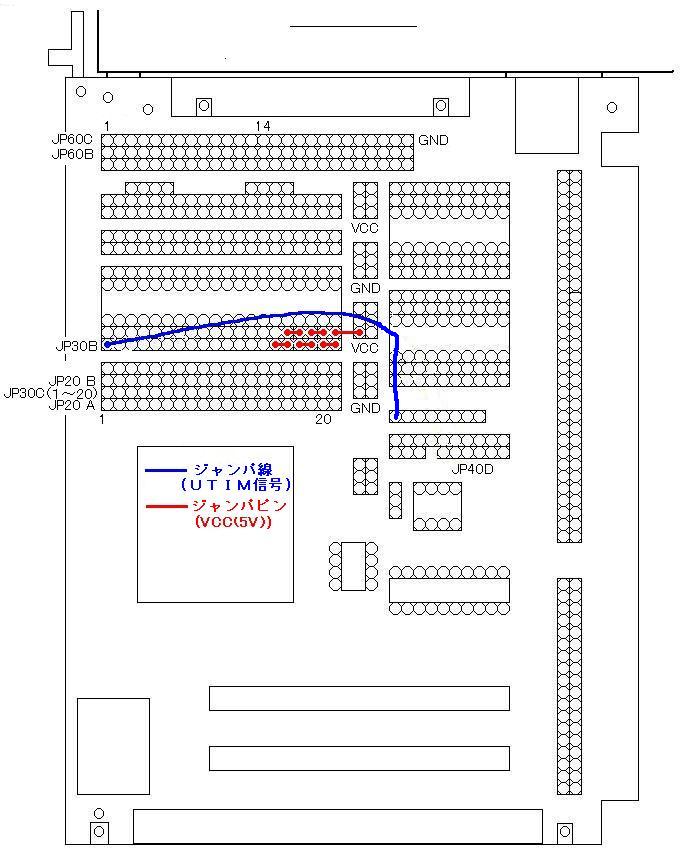

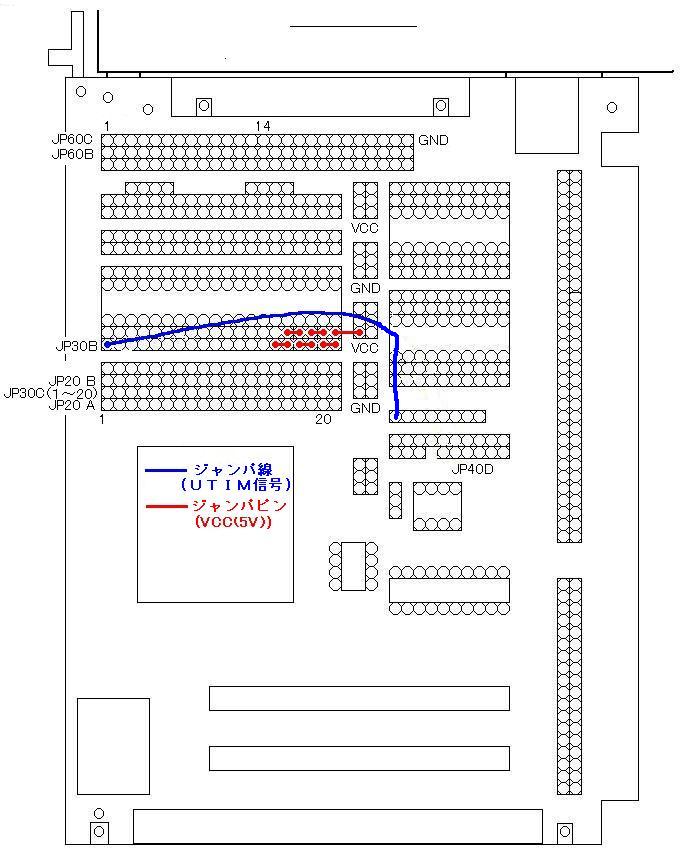

Fig.1 FPGAボードジャンパ設定図 (jamper.jpg)

- 必要物品

ショートピン(マイコンビルダ付属)、ジャンパ線(φ5mm)、ワイヤストリッパ

- 接続方法

- 隣り合った穴の接続

マイコンビルダ付属のショートピンで接続する。

- 離れたところの穴の接続

マイコンビルダ付属のジャンパ線をその長さにあわせて、切断し両端の被覆を約3ミリぐらいはがす。わかりやすいように必要に応じて色を変える。

- ○FPGAのピン割り振り

- コネクタ名称 : FPGA_JP20A (20pin ジャンパコネクタメス)

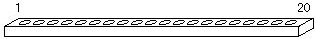

Figure.16_g_1 FPGA_JP20Aのコネクタ形状(jp20.jpg)

* コネクタの取りつけ位置、および方向はマイコンビルダー取扱説明書を参照。

Table.16_g_1 FPGA_JP20Aのインターフェース

ピン.No

|

信号名

|

I/O

|

備考

|

|

ピン.No

|

信号名

|

I/O

|

備考

|

1

|

-

|

-

|

未使用

|

|

11

|

TS1

|

IN

|

タッチセンサ信号 1

|

2

|

-

|

-

|

未使用

|

|

12

|

TS2

|

IN

|

タッチセンサ信号 2

|

3

|

-

|

-

|

未使用

|

|

13

|

TS3

|

IN

|

タッチセンサ信号 3

|

4

|

-

|

-

|

未使用

|

|

14

|

TS4

|

IN

|

タッチセンサ信号 4

|

5

|

-

|

-

|

未使用

|

|

15

|

TS5

|

IN

|

タッチセンサ信号 5

|

6

|

LS1

|

IN

|

白線感知センサ信号 1

|

|

16

|

TS6

|

IN

|

タッチセンサ信号 6

|

7

|

LS2

|

IN

|

白線感知センサ信号 2

|

|

17

|

R_DIR

|

OUT

|

MPC 右方向信号。オープンコレクタ出力

|

8

|

LS3

|

IN

|

白線感知センサ信号 3

|

|

18

|

R_PWM

|

OUT

|

MPC 右PWM信号。オープンコレクタ出力

|

9

|

LS4

|

IN

|

白線感知センサ信号 4

|

|

19

|

L_DIR

|

OUT

|

MPC 左方向信号。オープンコレクタ出力

|

10

|

LS5

|

IN

|

白線感知センサ信号 5

|

|

20

|

L_PWM

|

OUT

|

MPC 左PWM信号。オープンコレクタ出力

|

- コネクタ名称 : FPGA_JP30C (20pin ジャンパコネクタメス)

Figure.16_g_3 FPGA_JP30Cのコネクタ形状(jp20.jpg)

Table.16_g_3 FPGA_JP30Cのインターフェース

ピン.No

|

信号名

|

I/O

|

備考

|

|

ピン.No

|

信号名

|

I/O

|

備考

|

1

|

-

|

-

|

未使用

|

|

11

|

-

|

-

|

未使用

|

2

|

-

|

-

|

未使用

|

|

12

|

-

|

-

|

未使用

|

3

|

-

|

-

|

未使用

|

|

13

|

-

|

-

|

未使用

|

4

|

-

|

-

|

未使用

|

|

14

|

-

|

-

|

未使用

|

5

|

-

|

-

|

未使用

|

|

15

|

-

|

-

|

未使用

|

6

|

-

|

-

|

未使用

|

|

16

|

Vcc

|

-

|

5V

|

7

|

-

|

-

|

未使用

|

|

17

|

Vcc

|

-

|

5V

|

8

|

-

|

-

|

未使用

|

|

18

|

Vcc

|

-

|

5V

|

9

|

-

|

-

|

未使用

|

|

19

|

Vcc

|

-

|

5V

|

10

|

-

|

-

|

未使用

|

|

20

|

Vcc

|

-

|

5V

|

- コネクタ名称 : FPGA_JP20B (20pin ジャンパコネクタメス)

Figure.16_g_5 FPGA_JP20Bのコネクタ形状(jp20.jpg)

Table.16_g_5 FPGA_JP20Bのインターフェース

ピン.No

|

信号名

|

I/O

|

備考

|

|

ピン.No

|

信号名

|

I/O

|

備考

|

1

|

CH_AY

|

IN

|

ロータリーエンコーダY チャネルA

|

|

11

|

R/W

|

OUT

|

LCD リード・ライト

|

2

|

CH_BY

|

IN

|

ロータリーエンコーダY チャネルB

|

|

12

|

E

|

OUT

|

LCD イネーブル

|

3

|

CH_AX

|

IN

|

ロータリーエンコーダX チャネルA

|

|

13

|

DB0

|

INOUT

|

LCD データ 0

|

4

|

CH_BX

|

IN

|

ロータリーエンコーダX チャネルB

|

|

14

|

DB1

|

INOUT

|

LCD データ 1

|

5

|

-

|

-

|

未使用

|

|

15

|

DB2

|

INOUT

|

LCD データ 2

|

6

|

-

|

-

|

未使用

|

|

16

|

DB3

|

INOUT

|

LCD データ 3

|

7

|

PO

|

IN

|

パワーオン信号

|

|

17

|

DB4

|

INOUT

|

LCD データ 4

|

8

|

-

|

-

|

未使用

|

|

18

|

DB5

|

INOUT

|

LCD データ 5

|

9

|

-

|

-

|

未使用

|

|

19

|

DB6

|

INOUT

|

LCD データ 6

|

10

|

RS

|

OUT

|

LCD レジスタセレクト

|

|

20

|

DB7

|

INOUT

|

LCD データ 7

|

| |