|

- はじめに

この仕様書は、MIRS0003のFPGAボード内のFPGAチップに構成するロータリエンコーダモジュールの取扱方法と機能詳細を記載したものである。

- 取扱い説明

- Maxplus2での回路情報の呼び出し方法

- ダウンロードファイル

re_m.zip

- 手順

- 圧縮ファイル re_m.zipをダウンロードします。

- re_m.zip を適当なフォルダで解凍します。

- maxplus2でグラフィックエディタを開きます。

- 解凍ファイルの中にある re_m.sym をグラフィックエディタで部品として呼び出します。

- 圧縮ファイルの内容

re_m.zip には以下のファイルが入っています。

- rtencoder.vhd

- 機能構成図(Fig.1)に示す カウント回路ブロックのVHDLファイル

- rtencoder.sym

- カウント回路のブロックシンボル

- countcont.vhd

- 機能構成図(Fig.1)に示す カウント制御回路ブロックのVHDLファイル

- countcont.sym

- カウント制御回路のブロックシンボル

- resetcont.vhd

- 機能構成図(Fig.1)に示す リセット制御回路ブロックのVHDLファイル

- resetcont.sym

- リセット制御回路のブロックシンボル

- re_m.gdf

- ロータリエンコーダモジュール全体のグラフフィックエディタのファイル

- re_m.sym

- ロータリエンコーダモジュール全体のブロックシンボル

- 機能説明

- 機能概要

MIRS0003 FPGAボード モジュールはモータの回転数をカウントし、移動した距離の計測や自己位置を認識する行うためのものであり、FPGAボード内のFPGAチップに構成される。この機能を実現するためにMIRS0003 FPGAボード モジュールでは以下のような機能構成を持つ。

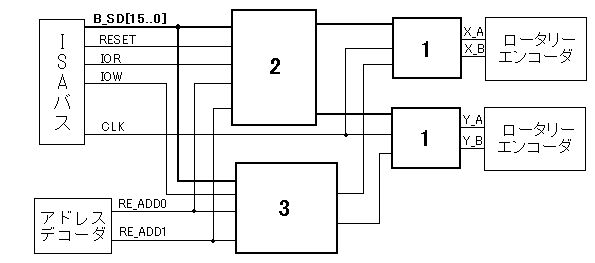

Fig.1 FPGAボード モジュールの機能構成図(re_m_block.jpg)

- カウント回路

この回路は、モータからの信号からモータの回転数をカウントする回路。

- カウント制御回路

この回路は、データ呼出し命令がきた時にをISAバスにカウントデータを送る機能を持つ。

- リセット制御回路

この回路は、リセット命令がきた時に実際にカウンタをリセットさせる信号を制御する回路

- 機能詳細

ロータリエンコーダモジュールでは、自己位置認識のためのモータの回転数をカウントする。モータのロータリエンコーダ部からA相、B相の90度ずれた矩形波が発生する。それをカウントすることによってモータの回転数を調べる。ロータエンコーダの詳しい説明はMIRSATLM ロータリエンコーダ技術資料(MIRSATLM-TECH-1001)を参照のこと

以下では、機能構成図(Fig.1)に示した各機能ブロックの詳細説明を行う。

- カウント回路

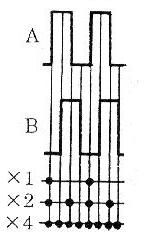

モータのロータリエンコーダ部からの信号から回転数を実際にカウントする回路。回転方向は、90度ずれた矩形波の変化する順番によって見分ける。カウントの方法には下図に示すように1、2、4逓倍のカウントの方法があるがこの回路では1逓倍でカウントする。また、負の数は補数表示となる。カウンタは16bitカウンタである。

- カウント制御回路

この回路は、アドレスが指定されかつ、読み取り命令がきたときバスにアドレスで指定されたカウンタの値を出力する働きを持つ。

それ以外の場合は、ハイインピーダンスを出力しておく。

- リセット制御回路

この回路はアドレスが指定されたとき、書き込み信号とモジュールセレクタ信号によって、カウンタをリセットする。

- インターフェース

Table 1 ロータリエンコーダモジュールのインターフェース

信号名

|

方 向

|

対 象

|

概 要

|

RE_ADD0

|

IN

|

アドレスデコーダ |

REモジュールセレクタ信号(Xカウンタ選択用)

|

RE_ADD1

|

IN

|

アドレスデコーダ |

REモジュールセレクタ信号(Yカウンタ選択用)

|

B_SD0

|

INOUT

|

ISAバス |

データバス

|

B_SD[1..15]

|

OUT

|

ISAバス |

15bit データバス

|

IOR

|

IN

|

ISAバス |

I/Oリード・ストローブ

|

IOW

|

IN

|

ISAバス |

I/Oライト・ストローブ

|

RESET

|

IN

|

ISAバス |

システムリセット

|

CLK

|

IN

|

ISAバス |

システムクロック 8MHz

|

X_A,X_B

|

IN

|

ロータリーエンコーダ |

Xカウンタ用2相信号入力端子

|

Y_A,Y_B

|

IN

|

ロータリーエンコーダ |

Yカウンタ用2相信号入力端子

|

|

|