係.丂俵俹倀偺挷嵏

[俇俉俲偺傾乕僉僥僋僠儍]

(1)丂俇俉俲偺摿挜

丂俇俉俲偵偼丄俁偮偺摿挜偑偁傞丅

丂戞堦偵丄僙僌儊儞僩偲偄偆奣擮偑側偄丅偦偺偨傔丄忢偵侾俇俵僶僀僩乮俀24僶僀僩乯偺儊儌儕嬻娫傪堦條偵傾僋僙僗偡傞帠偑偱偒傞丅偙傟偼丄婡婍慻傒崬傒梡偺俠俹倀偲偟偰戝偒側儊儌儕嬻娫偑偁傑傝栤戣偵側傜側偄偲偒偵丄梋寁側僆乕僶乕僿僢僪偑側偔丄搒崌偑傛偄丅

丂戞擇偵丄俇俉俲偺撪晹儗僕僗僞偼慡偰俁俀價僢僩偵側偭偰偄傞丅偙偺偨傔丄忚梋嶼傗傾僪儗僗寁嶼偑梕堈偵峴偊傞丅峏偵丄偦偺儗僕僗僞孮偼梡搑偵偮偄偰偁傑傝惂尷偑側偄斈梡儗僕僗僞曽幃傪偲偭偰偄偰丄儗僕僗僞娫偺僨乕僞揮憲傗僨乕僞偺僙乕僽丒儘乕僪偺夞悢偑彮側偔偰偡傓丅

丂戞嶰偵丄俇俉俲偼僗僞僢僋傗僉儏乕傪梡偄偨墘嶼張棟儖乕僠儞偺婰弎偑梕堈側柦椷僙僢僩偲傾僪儗僢僔儞僌儌乕僪傪帩偭偰偄傞丅偙傟偼丄俠傗俹倎倱們倎倢側偳偺峔憿壔僾儘僌儔儈儞僌尵岅偺幚峴偵嵺偟丄搒崌偑傛偄丅傑偨丄斈梡儗僕僗僞曽幃傪偲偭偰偄傞偨傔丄摨帪偵暋悢屄偺僗僞僢僋傪娗棟偱偒傞丅

(2)丂俇俉俲偺儗僕僗僞孮

- 傾僪儗僗儗僕僗僞乮俙侽乣俙俈乯

- 丂傾僪儗僗儗僕僗僞偼丄傾僪儗僗儀乕僗偵巊偆帠傪栚揑偲偟偰偄傞偺偱丄傾僪儗僔儞僌儌乕僪偑偨偔偝傫嶌傜傟偰偄傞丅俙侽乣俙俇傑偱偑傾僪儗僗儗僕僗僞丄俙俈偼棤昞偵暘偐傟偰偄偰丄偦傟偧傟僗乕僷乕僶僀僓梡偺僗僞僢僋億僀儞僞乮俽俽俹乯丆儐乕僓梡偺僗僞僢僋億僀儞僞乮倀俽俹乯偲偟偰巊梡偝傟傞丅

- 僨乕僞儗僕僗僞乮俢侽乣俢俈乯

- 丂僨乕僞儗僕僗僞偼丄偄傢備傞傾僉儏儉儗乕僞偲偟偰巊偆偺偵曋棙偵偱偒偰偄偰丄壓偐傜俉價僢僩媦傃侾俇價僢僩偵愗偭偰傕巊偊傞丅乮壓偺俉價僢僩偵僨乕僞傪儘乕僪偟偨帪丄忋偺俀係價僢僩偼曄壔偟側偄丅乯

- 僾儘僌儔儉僇僂儞僞乮俹俠乯

- 丂俹俠偼俁俀價僢僩偱偁傞丅偟偐偟丄巊梡偱偒傞偺偼壓埵俀係價僢僩側偺偱丄傾僪儗僗嬻娫偼侾俇俵僶僀僩偱偁傞丅

- 僗僥乕僞僗儗僕僗僞乮俽俼乯

- 丂俽俼偼侾俇價僢僩挿偱丄忋埵敿暘偼僔僗僥儉僶僀僩丄壓埵敿暘偼儐乕僓僶僀僩偲側偭偰偄傞丅僔僗僥儉僶僀僩偼僔僗僥儉偺忬懺傪帵偟丄儐乕僓僗僥乕僩偺偲偒偼偙撪梕傪彂偒姺偊傜傟側偄丅儐乕僓僶僀僩偼倅俉侽偺俥儗僕僗僞偺傛偆側傕偺偱偁傞丅

(3)丂僗乕僷僶僀僓僗僥乕僩丒儐乕僓僗僥乕僩

丂俇俉俲偼俷俽偺懚嵼傪慜採偲偟偰偄傞偨傔丄僔僗僥儉僾儘僌儔儉偑帒尮娗棟側偳偺憖嶌傪偡傞偙偲偑偱偒傞傛偆偵丄幚峴帪偺忬懺偑僗乕僷僶僀僓僗僥乕僩偲儐乕僓僗僥乕僩偵暘偐傟偰偄傞丅

|

| 恾侾丂68k偺儗僕僗僞峔惉 |

- 摿尃柦椷

- 丂僗乕僷僶僀僓僗僥乕僩偱偟偐幚峴偱偒側偄柦椷丅俽俼偺僔僗僥儉僶僀僩偺曄峏傗丄妱崬傒張棟偵娭偡傞柦椷孮丅

(4)丂俇俉俲偺僨乕僞宆

丂俇俉俲偼丄侾價僢僩乮價僢僩僨乕僞乯丄係價僢僩乮俛俠俢僨乕僞乯丄8價僢僩乮僶僀僩僨乕僞乯丄侾俇價僢僩乮儚乕僪僨乕僞乯丄俁俀價僢僩乮儘儞僌儚乕僪僨乕僞乯偺僨乕僞傪庢傝埖偆偙偲偑偱偒傞丅

- 儗僕僗僞

- 丂僨乕僞儗僕僗僞偼係庬椶偺挿偝偺僨乕僞傪慡偰曐帩偡傞偙偲偑偱偒傞丅傾僪儗僗儗僕僗僞偼侾俇價僢僩枖偼俁俀價僢僩傪扨埵偲偟偰埖偆丅

- 儊儌儕

- 丂僨乕僞傪儊儌儕偵婰壇偝偣傞応崌偼儚乕僪乮俀價僢僩乯傪扨埵偲偡傞丅偙偺嵺丄掅傾僪儗僗懁偵忋埵僶僀僩偺僨乕僞傪丄崅傾僪儗僗懁偵壓埵僶僀僩偺僨乕僞傪擺傔傞丅

[傾僪儗僔儞僌儌乕僪]

(1)丂僆儁儔儞僪偺庬椶

丂僜乕僗僆儁儔儞僪丒丒丒僨乕僞傪嫙媼偡傞丅

丂僨僗僥傿僱乕僔儑儞僆儁儔儞僪丒丒丒僨乕僞傪庴偗擖傟傞丅

丂僜乕僗偑僨乕僞偦偺傕偺偵拲栚偟偰偄傞偺偵懳偟丄僨僗僥傿僱乕僔儑儞偼撪梕偩偗偱側偔偦偺応強偵傕廳梫惈偑偁傞丅

(2)丂僆儁儔儞僪偺巜掕

丂僆儁儔儞僪偲偟偰巜掕偝傟偆傞傕偺偼丄奺庬儗僕僗僞偲儊儌儕撪偺斣抧偱偁傞丅偙偆偄偭偨傕偺傪僆儁儔儞僪偲偟偰巜掕偡傞曽朄偼偄偔偮偐偁傝丄偙傟傜傪傾僪儗僔儞僌儌乕僪偲屇傇丅

丂僆儁儔儞僪偲偟偰儗僕僗僞傪巊偆嵺偵偼丄扨偵偦偺儗僕僗僞偺柤慜傪巜掕偡傟偽傛偄丅儊儌儕傾僪儗僗偵偮偄偰偼丄僾儘僌儔儉幚峴帪偵偄偔偮偐偺儗僕僗僞傗掕悢傪巊偭偰儊儌儕傾僪儗僗傪寁嶼偟丄偦偺抣傪僆儁儔儞僩偲偟偰巜掕偡傞偙偲偑偱偒傞丅偙偺帪偺寁嶼傪傾僪儗僗寁嶼丄寁嶼偺寢壥摼傜傟偨儊儌儕斣抧傪幚峴傾僪儗僗偲偄偆丅

[僀儞僗僩儔僋僔儑儞僙僢僩]

俇俉俲偺帩偮柦椷僙僢僩偼丄師偺傛偆偵暘椶偱偒傞丅

丂乮侾乯嶼弍墘嶼丂乮俀乯榑棟墘嶼丂乮俁乯僔僼僩乛儘乕僥乕僩

丂乮係乯價僢僩憖嶌丂乮俆乯俛俠俢墘嶼丂乮俇乯僨乕僞堏摦

丂乮俈乯僕儍儞僾乛僐乕儖丂乮俉乯僔僗僥儉惂屼

(1)丂嶼弍墘嶼

丂嶼弍墘嶼偵偼丄壛尭忚梋偺懠偵丄斾妑丄僋儕傾丄僱僎乕僩側偳偑偁傞丅忚梋嶼偵偼晞崋偁傝偲晞崋側偟偺椉曽偑梡堄偝傟偰偄傞丅偙傟傜偺墘嶼偼丄傾僪儗僗偵懳偟偰偼丄侾俇枖偼俁俀價僢僩偱僨乕僞偵懳偟偰偼偡傋偰偺僆傌儔儞僪僒僀僘偱巊梡偱偒傞丅

(2)丂榑棟墘嶼

丂榑棟墘嶼偵偼丄俙俶俢丆俷俼丆俤俷俼丆俶俷俿偑偁傝丄慜嶰幰偵偮偄偰偼懄抣傪巊偆柦椷乮俙俶俢倢丆俷俼倢丆俤俷俼倢乯偑偁傞丅傾僪儗僔儞僌儌乕僪偺巜掕偵傛傝丄偙傟傜傢俽俼傪僨僗僥傿僱乕僔儑儞偲偡傞偙偲偑偱偒傞丅

(3)丂僔僼僩乛儘乕僥乕僩

丂僔僼僩偲儘乕僥乕僩偼丄儗僕僗僞偵懳偟偰傕丄儊儌儕偵懳偟偰傕幚峴偱偒傞丅扐偟丄儊儌儕撪偺僨乕僞偵懳偟偰偼侾俇價僢僩僆儁儔儞僪偱侾價僢僩偺僔僼僩偵尷傜傟傞丅

(4)丂價僢僩憖嶌

丂價僢僩憖嶌偼價僢僩僥僗僩偲僥僗僩偟偨價僢僩偵懳偟偰峴偆憖嶌偲偺慻傒偱偁傞丅

- 價僢僩僥僗僩

- 丂巜掕偝傟偨價僢僩偑乭侽乭側傜丄倅僼儔僌傪棫偰傞丅

- 僥僗僩屻偺憖嶌

- 丂僥僗僩屻偺憖嶌偵偼丄俛俿俽俿乮壗傕偟側偄乯丄俛俽俤俿乮侾偵偡傞乯丄俛俠俴俼乮侽偵偡傞乯丄俛俠俫俧乮斀揮偡傞乯偑偁傞丅

(5)丂俛俠俢墘嶼

丂俛俠俢墘嶼偼壛尭嶼乮俙俛俠俢乯偲晞崋斀揮乮俶俛俠俢乯偑偁傞丅堦搙偵埖偊傞僆儁儔儞僪僒僀僘偼俉價僢僩偱偁傞丅

(6)丂僨乕僞堏摦

丂傎偲傫偳偺僨乕僞堏摦偵娭偡傞僾儘僌儔儉偼俵俷倁俤柦椷偵傛偭偰峴傢傟傞丅俵俷倁俤柦椷偼丄僜乕僗丄僨僗僥傿僱乕僔儑儞偲傕俇價僢僩偱巜掕偝傟傞丅

(7)丂僕儍儞僾乛僐乕儖

丂僕儍儞僾丒僐乕儖偵偼丄柍忦審暘婒丄忦審暘婒偺俀偮偑偁傝丄懠偵傕庤懕偒偺屇傃弌偟丄庤懕偒偐傜偺暅婣偑偁傞丅

(8)丂僔僗僥儉惂屼

丂僔僗僥儉惂屼偺柦椷偵偼丄摿尃柦椷丄僩儔僢僾柦椷丄媦傃俽俼偺僔僗僥儉僶僀僩傪憖嶌偡傞柦椷偑偁傞丅

[惂屼梡俇俉俲儃乕僪]

丂庬乆偺傾僋僠儏僄乕僞媦傃僙儞僒乕摍傪僐儞僩儘乕儖偡傞偨傔偵彫宆婎斦忋乮侾俀們倣亊侾俀們倣乯偵崅枾搙偱幚憰偝傟偨彫宆俇俉俲儃乕僪偱偁傞丅摨帪偵丄僶僢僥儕乕嬱摦傪慜採偲偟偰偄傞偨傔丄僴僀僗僺乕僪俠亅俵俷俽傪巊梡偟偨徣揹椡宆偺儃乕僪僐儞僺儏乕僞偱偁傞丅

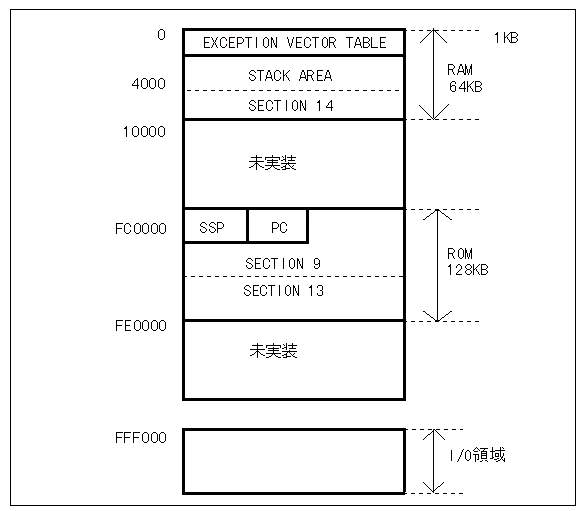

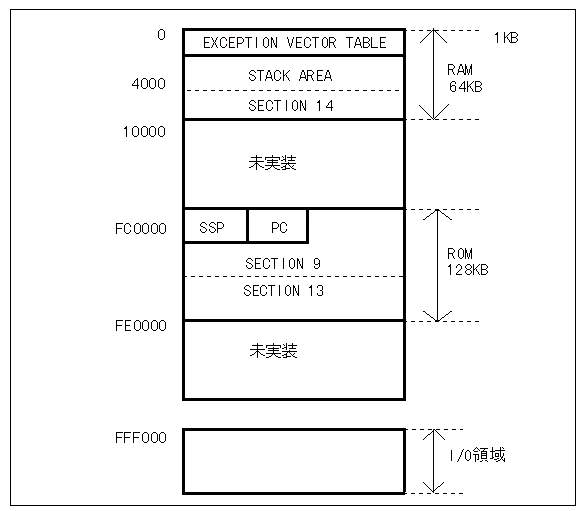

丂恾俀偵帵偡傛偆偵丄俇俉俲儃乕僪偼俵俹倀儃乕僪偲俬乛俷儃乕僪偺擇枃堦慻偱峔惉偝傟傞俬乛俷僐儞僩儘乕儖巜岦偺僔僗僥儉峔惉偲側偭偰偄傞丅偝傜偵昞侾偵帵偡俉侽俹儅僓乕僶僗僐僱僋僞偵僔僗僥儉僶僗傪奐曻偟偰偄傞偨傔丄昁梫偵墳偠偰奼挘偡傞偙偲偑弌棃傞丅

丂杮僔僗僥儉偺儊儌儕乕儅僢僾傪恾俁偵帵偡丅杮僔僗僥儉偼丄揹尮僆儞枖偼奜晹儕僙僢僩偵傛傝丄俼俷俵椞堟偺愭摢斣抧俥俠侽侽侽侽偐傜俀儚乕僪傪偦傟偧傟俽俽俹偍傛傃俹俠偲偟偰庢傝崬傒丄俹俠偵彂偐傟偨儊僀儞僄儞僩儕乕儖乕僠儞偺僄儞僩儕乕億僀儞僩偐傜僾儘僌儔儉傪幚峴偡傞傛偆偵側偭偰偄傞丅

丂傑偨丄杮僔僗僥儉偱偼丄斈梡僀儞僥乕僼僃乕僗俴俽俬乮俹俬乛俿媦傃俁屄偺俹俬俙乯傪搵嵹偟丄奺俴俽俬偺妱崬傒梫媮抂巕傪奐曻偟偰乮恾係偵帵偡俰俹侾偵傛傝妱傝崬傒儗儀儖慖戰壜丄僆乕僩儀僋僞妱傝崬傒乯丄懡條側儌乕僪偱偺俬乛俷僐儞僩儘乕儖傪壜擻偲偟偰偄傞丅恾俆乣俈偵奺俬乛俷僐僱僋僞偺僺儞丒傾僒僀儞傪帵偡丅

丂偝傜偵丄俹俬乛俿偵傛傝僞僀儅妱傝崬傒乮儗儀儖俆僆乕僩儀僋僞乯傪壜擻偲偟偰偄傞丅

|

| 恾俀儊儌儕乕儅僢僾 |

[晅榐]

- 傾乕僉僥僋僠儍

- 丂柦椷偺婡擻丄僨乕僞偺昞尰婡擻摍偺丄僴乕僪僂僃傾偲僜僼僩僂僃傾偺奐敪偵昁梫偲側傞僴乕僪僂僃傾偺巇條偺偙偲丅

- 僙僌儊儞僩

- 丂僾儘僌儔儉偑戝偒偔偰堦搙偵庡婰壇偵奿擺偱偒側偄応崌丄傑偨偼庡婰壇憰抲傪桳岠偵巊偆偨傔偵僾儘僌儔儉傪儌僕儏乕儖壔偡傞応崌偵丄嵶暘壔偝傟傞僾儘僌儔儉偺奺晹暘丅

- 僆乕僶乕僿僢僪

- 丂柍懯偵旓傗偝傟傞帪娫傑偨偼婰壇椞堟丅庡偵丄俷俽偑懚嵼偟偰偄傞椞堟傗丄偦傟偑摥偄偰偄傞帪娫傪偝偡応崌偑懡偄丅

- 僉儏乕

- 丂張棟偑俥俬俥俷乮俥倝倰倱倲丂俬値丂俥倝倰倱倲丂俷倳倲乯偱偁傞僨乕僞偺廤傑傝偺峔憿丅懸偪峴楍偲傕偄偆丅

- 傾僉儏乕儉儗乕僞

- 丂墘嶼晹傪峔惉偡傞庡梫側儗僕僗僞偺堦偮偱偁傝丄嶼弍墘嶼傗榑棟墘嶼傪峴偆僨乕僞傪婰壇偟偨傝丄墘嶼偺寢壥傪挋偊偰偍偄偨傝偡傞応強丅

- 僼僃僢僠

- 丂俠俹倀偑柦椷傪庢傝弌偡偙偲丅

- 傾僋僲儕僢僕

- 丂僨乕僞捠怣傪峴偆嵺偵丄僨乕僞偑惓偟偔憲傜傟偨偙偲傪丄庴怣懁偑憲怣懁傊曬崘偡傞偙偲丅

[堷梡]

丂丂丂丂丂丂俵俹倀偺挷嵏丂丂丂moon:/mirsdoc/mirs94/mirs9401/memo/mpu.sam