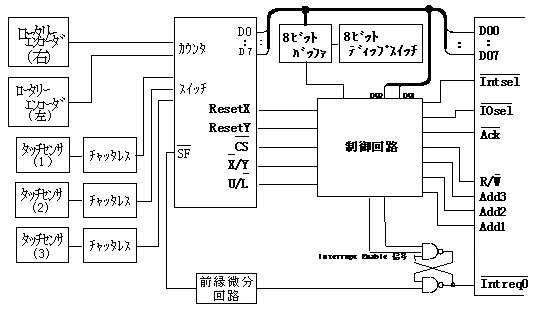

ロータリエンコーダ信号処理回路

ロータリエンコーダ信号処理回路は、ロータリエンコーダの2相の信号からロータリエンコーダの回転数と回転方向を測定し、CPUの命令にしたがってデータの出力を行う。

回路はロータリエンコーダ接続回路とカウンタ回路、カウンタリセット回路から成る。

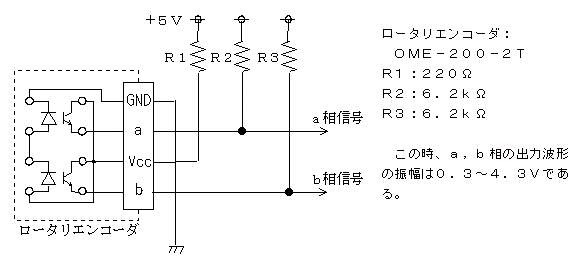

|

| 図1 ロータリエンコーダ接続回 |

ロータリエンコーダ接続回路はロータリエンコーダの出力波形が論理回路の”H”、”L”レベルを満足するように振幅を設定するためのものである。この回路は、使用するロータリエンコーダに合わせて設計する必要がある。図1にロータリエンコーダ接続回路を示す。

1・2 タッチセンサの機能

《タッチセンサ信号処理回路》

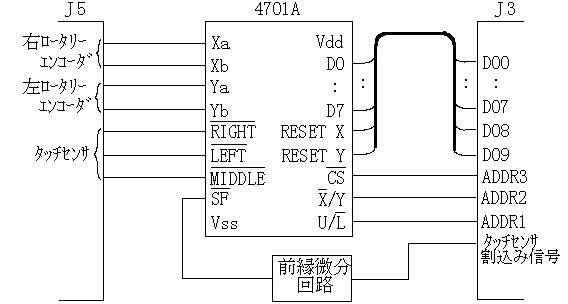

タッチセンサ信号処理回路は、タッチセンサの信号からスイッチ割り込みの割込み要求を行う。回路は、タッチセンサのチャタリング防止回路と割込み信号発生回路、タッチセンサステータス出力回路、割込みVECTOR発生回路から成る。

タッチセンサの信号処理にも、μPD4701Aを利用する。タッチセンサはSR-FFを用いてチャタリングを除去し、その信号をμPD4701Aに取り込む。そして、μPD4701Aの持つスイッチフラグ信号を利用して割込み信号発生回路で割込み信号を発生させる。タッチセンサの状態は、μPD4701Aのカウント値とまとめて出力される為、別に、タッチセンサステータス出力回路を設計する必要はない。

割込みVECTOR発生回路は、割込みサイクル時にVIPC310-IP間のデータバス(Internal Data Bus)に8ビットの割込みVECTORを載せる回路である。IPからデータバスには通常μPD4701Aの出力データが載せられる為、バス上にμPD4701Aの出力データと割込みVECTORが同時に載るようなことの無いよう、3ステートのバッファを用いて割込みVECTORの出力を制御する。割込みVECTORの設定は、8ビットディップスイッチによって行う。IPをVIPC310に搭載するとき、両者は互いにボードの部品面を向かい合わせる事になる。IPをVIPC310に搭載したまま割込みVECTORの設定を行えるよう、ディップスイッチは横向きのものを使用した。

2、概要

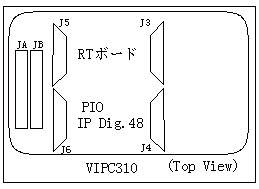

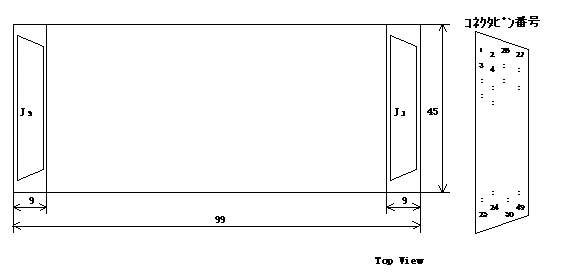

ロータリーエンコーダ、タッチセンサボード(以後RTボードと呼ぶ)は,Industry-Packの形にする。IndustryPackとは、VIPC310に直接載せるもので、RTボード以外には、PIO IP-Dig.48がある。

RTボードは,VIPC310のコネクタJ3とJ5に取り付ける(図2)。J3にはInternalData Bus、Address、制御用信号線、等があり、VIPC310を介してRTボードとVSBC-1(CPU)とのやり取りを行う。J5は直接JAとつながっており、ここからロータリーエンコーダのパルス信号およびタッチセンサスイッチデータを取り込む。

|

| 図2 RTボード |

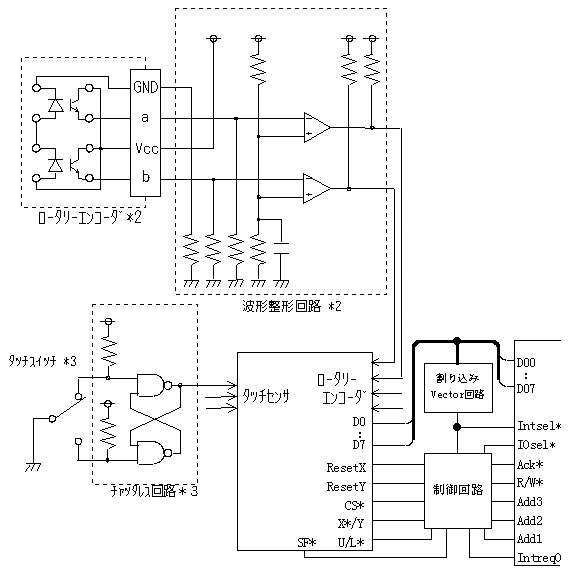

2・1 回路構成

以下に回路構成を示す。

|

| 回路1 |

リードサイクル

| A8 | A7 | A6-A4 | A3 | A2 | A1 | A0 | D00-D07 |

| 0 | 0 | 未使用 | 0 | 0 | 0 | 0 | 右ロータリーエンコーダ下位8ビット |

| 0 | 0 | 未使用 | 0 | 0 | 1 | 0 | 右ロータリーエンコーダ上位8ビット |

| 0 | 0 | 未使用 | 0 | 1 | 0 | 0 | 左ロータリーエンコーダ下位8ビット |

| 0 | <0/TD> | 未使用 | 0 | 1 | 1 | 0 | 左ロータリーエンコーダ上位8ビット |

リセットサイクル

| A8 | A7 | A6-A4 | A3 | A2 | A1 | A0 | D08 | D09 | |

| 0 | 0 | 未使用 | 1 | 0 | 0 | 0 | 0 | 1 | 右カウンタ |

| 0 | 0 | 未使用 | 1 | 0 | 0 | 0 | 1 | 0 | 左カウンタ |

| 0 | 0 | 未使用 | 1 | 0 | 0 | 0 | 1 | 1 | 両カウンタ |

|

| 回路2 |

|

| 回路3 |

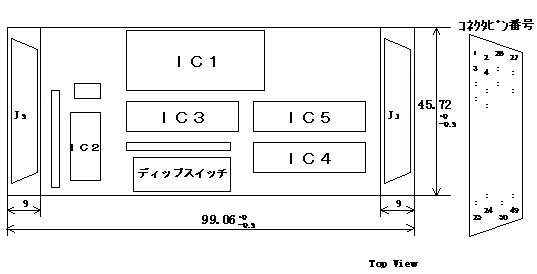

2・2外形

|

|

| ロータリエンコーダ・ボード外観図 |

2・3インターフェス

以下に各ピンのピンアサインを示す。 コネクタJ3

| No. | 信号名 | 方向 | 内容 | 備考 |

| 1 | GND | -- | GND | |

| 2 | CLK | ← | Clock 8MHz | |

| 3 | BRESET* | ←CPUリセット信号 | ||

| 4 | D00 | ←→ | DATA 2^0 | |

| 5 | D01 | ←→ | DATA 2^1 | |

| 6 | D02 | ←→ | DATA 2^2 | |

| 7 | D03 | ←→ | DATA 2^3 | |

| 8 | D04 | ←→ | DATA 2^4 | |

| 9 | D05 | ←→ | DATA 2^5 | |

| 10 | D06 | ←→ | DATA 2^6 | |

| 11 | D07 | ←→ | DATA 2^7 | |

| 12 | D08 | ←→ | DATA 2^8 | 未使用 |

| 13 | D09 | ←→ | DATA 2^9 | 未使用 |

| 14 | D10 | ←→ | DATA 2^10 | 未使用 |

| 15 | D11 | ←→ | DATA 2^11 | 未使用 |

| 16 | D12 | ←→ | DATA 2^12 | 未使用 |

| 17 | D13 | ←→ | DATA 2^13 | 未使用 |

| 18 | D14 | ←→ | DATA 2^14 | 未使用 |

| 19 | D15 | ←→ | DATA 2^15 | 未使用 |

| 20 | BS0* | ← | Byte Select (下位バイト) | BS0*=0 (active) |

| 21 | BS1* | ← | Byte Select (上位バイト) | BS1*=1 (negative) |

| 22 | V- | -- | 電源-12V | 未使用 |

| 23 | V+ | -- | 電源+12V | 未使用 |

| 24 | Vcc | -- | 電源+5V | |

| 25 | GND | -- | GND | |

| 26 | GND | -- | GND | |

| 27 | Vcc | -- | 電源+5V | |

| 28 | PWR* | ← | Read*Write Select | 1=Read,0=Write |

| 29 | IDA* | ← | ID PROM Select 信号 | |

| 30 | H1 | ← | high level 入力 | |

| 31 | MEMSELA* | ← | Memory R*W Cycle 信号 | 未使用 |

| 32 | H2 | ← | high level 入力 | |

| 33 | INTSELA* | ← | Interrupt Cycle 信号 | |

| 34 | H3 | ← | high level 入力 | |

| 35 | IOSELA* | ← | I/O Cycle 信号 | |

| 36 | H4 | ← | high level 入力 | |

| 37 | ADDR1 | ← | Address 2^1 | |

| 38 | H5 | ← | high level 入力 | |

| 39 | ADDR2 | ←Address 2^2 | ||

| 40 | H6 | ← | high level 入力 | |

| 41 | ADDR3 | ← | Address 2^3 | |

| 42 | IRQA0* | → | Interrupt 信号 (割込み level=4) | |

| 43 | ADDR4 | ← | Address 2^4 | |

| 44 | IRQA1* | → | Interrupt 信号 (割込み level=5) | 未使用 |

| 45 | ADDR5 | ← | Address 2^5 | |

| 46 | H7 | ← | high level 入力 | high level 入力 |

| 47 | ADDR6 | ← | Address 2^6 | |

| 48 | ACKA* | → | Acknowledge | |

| 49 | +5PSTBT | -- | VIPC310ボードのバッテリー電源 | データ保存用、未使用 |

| 50 | GND | -- | GND |

コネクタJ5

| No. | 信号名 | 方向 | 内容 | 備考 |

| 1 | GND | -- | GND | |

| 2 | GND | -- | GND | |

| 3 | GND | -- | GND | |

| 4 | GND | -- | GND | |

| 5 | GND | -- | GND | |

| 6 | GND | -- | GND | |

| 7 | GND | -- | GND | |

| 8 | GND | -- | GND | |

| 9 | GND | -- | GND | |

| 10 | GND | -- | GND | |

| 11 | GND | -- | GND | |

| 12 | GND | -- | GND | |

| 13 | GND | -- | GND | |

| 14 | GND | -- | GND | |

| 15 | GND | -- | GND | |

| 16 | GND | -- | GND | |

| 17 | GND | -- | GND | |

| 18 | GND | -- | GND | |

| 19 | GND | -- | GND | |

| 20 | GND | -- | GND | |

| 21 | GND | -- | GND | |

| 22 | GND | -- | GND | |

| 23 | GND | -- | GND | |

| 24 | GND | -- | GND | |

| 25 | GND | -- | GND | |

| 26 | GND | -- | GND | |

| 27 | RRa | ← | 右ロータリ・エンコーダa相信号 | |

| 28 | GND | -- | GND | |

| 29 | Vcc | -- | 電源+5V | |

| 30 | GND | -- | GND | |

| 31 | RRb | ← | 右ロータリ・エンコーダb相信号 | |

| 32 | GND | -- | GND | |

| 33 | RLa | ← | 左ロータリ・エンコーダa相信号 | |

| 34 | GND | -- | GND | |

| 35 | Vcc | -- | 電源+5V | |

| 36 | GND | -- | GND | |

| 37 | RLb | ← | 左ロータリ・エンコーダb相信号 | |

| 38 | GND | -- | GND | |

| 39 | TRs* | ← | 右タッチセンサON信号 | |

| 40 | GND | -- | GND | |

| 41 | TRr* | ← | 右タッチセンサOFF信号 | |

| 42 | GND | -- | GND | |

| 43 | TMs* | ← | 中央タッチセンサON信号 | |

| 44 | GND | -- | GND | |

| 45 | TMr* | ← | 中央タッチセンサOFF信号 | |

| 46 | GND | -- | GND | |

| 47 | TLs* | ← | 左タッチセンサON信号 | |

| 48 | GND | -- | GND | |

| 49 | TLr* | ← | 左タッチセンサOFF信号 | |

| 50 | GND | -- | GND |

3、ソフトウェアビジビリティー

次にソフトウェアからの見え方を示す。

| Address A8A7A6A5A4A3A2A1A0 | Read/Write | DATA D7 D6 D5 D4 D3 D2 D1 D0 | MEMO |

| 0 x x x x 0 0 0 1 | Read | 2^7 2^6 2^5 2^4 2^3 2^2 2^1 2^0 右ロータリ・エンコーダカウンタ下位8ビット | 一定時間毎読む |

| 0 x x x x 0 0 1 1 | Read | SF L R M 2^11 2^10 2^9 2^8 右ロータリ・エンコーダカウンタ上位4ビット +スイッチデータ | SF:スイッチフラグ (SF=L+R+M,active high) L:左スイッチ(active high) R:右スイッチ(active high) M:中央スイッチ(active high) 一定時間毎、スイッチ割込み時に読む |

| 0 x x x x 0 1 0 1 | Read | 2^7 2^6 2^5 2^4 2^3 2^2 2^1 2^0 左ロータリ・エンコーダカウンタ下位8ビット | 一定時間毎読む |

| 0 x x x x 0 1 1 1 | Read | SF L R M 2^11 2^10 2^9 2^8 左ロータリ・エンコーダカウンタ上位4ビット +スイッチデータ | SF:スイッチフラグ (SF=L+R+M,active high) L:左スイッチ(active high) R:右スイッチ(active high) M:中央スイッチ(active high) 一定時間毎、スイッチ割込み時に読む |

| 0 x x x x 1 0 0 1 | Write | (カウンタリセット) x x x x x x 0 1 x x x x x x 1 0 左ロータリ・エンコーダカウンタリセット \ x x x x x x 1 1 左右カウンタ同時リセット | 右カウンタ読み込み後に行う 左カウンタ読み込み後に行う スタート時に行う |

| 0 x x x x 1 0 1 1 | Write | (割込みenable) x x x x x x x 0 割込み不可 x x x x x x x 1 割込み許可 | リセット後に行う |

※ アドレスおよびデータの "x" は、don't care を意味する。

4、部品表

初版基板の部品表はV94-CARD-301である。