マンマシンI/F

機能概要

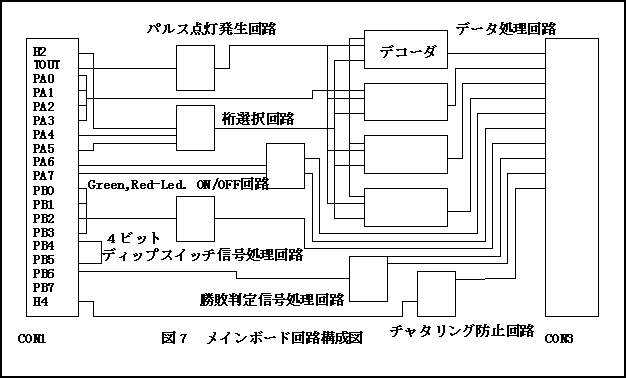

- MMIボードの回路は、

- 1、パルス点灯発生回路

- 2、桁選択回路

- 3、勝敗判定信号処理回路

- 4、チャタリング防止回路

- 5、データラッチON/OFF及びデータ処理回路の5個に分ける事ができる。

1、パルス点灯発生回路について

- この回路は、IC1、IC3、IC14からなり、下位の桁から順に上位の桁へと、

パルス信号を送る。これは、MC14513Bの入力が、ロウレベルになると、

他入力に関係なく(ただし、のみハイレベル)、全セグメント出力がブランク

(非点灯)になることを利用するためである。

2、桁選択回路について

- この回路は、IC6からなり、2進2ビットのデータ書き込み桁選択信号を各桁のデータラッチON/OFF回路へと振り分ける働きをする。

3、勝敗判定信号処理回路について

- この回路は、IC2、IC14からなり、勝敗判定装置からのON/OFF信号を電気的に絶縁し、CPUボードに送る働きをする。

4、チャタリング防止回路について

- この回路は、IC15からなり、フロントボードの押しボタンスイッチからの信号のチャタリングを防止し、CPUボードに送る働きをする。

5、データラッチON/OFF及びデータ処理回路

- まず、データラッチON/OFF回路は、IC7、IC8からなり、桁選択回路からの桁選択信号とHandshake 2からの信号によってデータを書き込むデコーダのラッチ機能をOFFし、データが書き込まれた後ラッチ機能をONさせる。つぎに、データ処理回路であるが、これは、IC9~IC12からなり、BCDコードで入力されたデータを7Seg.-Led.用の信号に変換する。また、そのデータをラッチする働きも持つ.

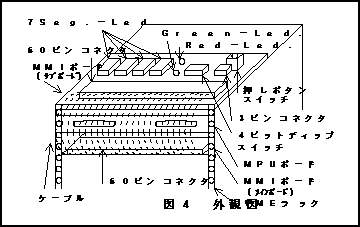

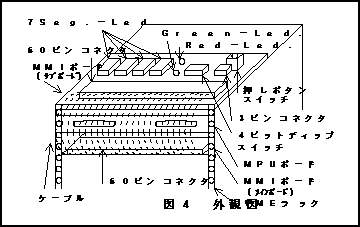

- MMIボードの主な仕様は、図4にあるように7Seg.-Led.(データ表示用)が4個、4ビットディップスイッチ(モード設定用)が1個、Green,Red-Led.(状態表示用)が各1個、押しボタンスイッチ(表示切替用)が1個である。

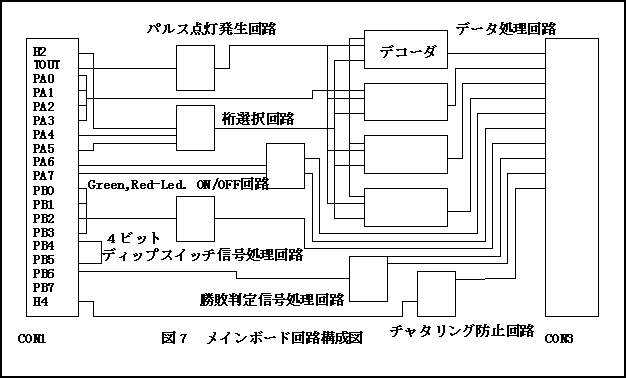

- 回路構成

- 図7は、メインボードの回路構成図である。ここでは、メインボードの回路を7つに分けてそれぞれの回路の機能等について説明する。

- ・パルス点灯発生回路

- いままでのマン・マシン・インタフェースボードでは、7Seg.-Led.の数が少なく、あまり多くの情報を一度に表示することができなかった。今回M MIボードでは、7Seg.-Led.の数を4個にした。普通に表示を制御す るには各Led.で4ビット合計16ビット必要であるが、ポートの制限もあり、図7の回路構成図にあるように68230のAポートの8ビットのうちPA0~PA5までの6ビットを使って表示をするようにした。そこで、ラッチ機能を持つデコーダを使用することにし、6ビットのうちの4ビットをLed.のデータ用に使い、残りの2ビットを桁の選択用に使うように工夫した。

ここで、問題となったのは、7Seg.-Led.の消費電流の増加である。Led.の消費電流は、1segment当り約20mAなので7Seg.-Led.が全部点灯したとすると約0.56Aもの電流が流れることになる。これは、電池で駆動するMIRSシステムにとっては大きな負荷になる。

そこで4つの位相の異なる方形波を作り、7Seg.-Led.をパルス点灯させることにより消費電流を約1/4にするようにした。一つの桁が点灯して再 び点灯する間隔が短い為、見た目には、すべての桁が点灯しているように見える。 また、これにより7Seg.-Led.の電流は、最大で約0.14Aになる。

この回路は、74LS161(4ビットバイナリ(2進化16進)カウンタ)、74LS00(2入力NANDゲート)、74LS08(2入力ANDゲート) からなり、7Seg.-Led.の下位の桁から順に上位の桁へと、パルス信号 を送る機能を持つ。

表示試験の結果、ちらつきが気にならなくなるのは約200Hz以上の時であった。この信号は、MC14513Bのに入力される。これは、入力が、ロウレベルになると、他入力に関係なく(ただし、のみハイレベル)、全セグメント出力がブランク(非点灯)になることを利用するためである。

- ・桁選択回路

- この回路は、74LS04(NOTゲート)からなり、2進2ビットのデータ書き込み桁選択信号を各桁のデータラッチON/OFF回路へと振り分ける機能を持つ。

- ・勝敗判定信号処理回路

- この回路は、74LS14(インバータシュミットトリガ)、PC817(光アイソレータ)からなり、勝敗判定装置からのON/OFF信号を電気的に絶縁し、レベルの判別をしてCPUボードに送る機能を持つ。(付録:回路図参照)

また、勝敗判定装置とは、フロントボードの3ピンコネクタを用い接続される。

- ・チャタリング防止回路

- この回路は、74LS00(2入力NANDゲート)からなり、フロントボードの押しボタンスイッチからの信号のチャタリングを防止し、CPUボードに機能を持つ。

- ・データラッチON/OFF及びデータ処理回路

- データラッチON/OFF回路は、74LS10(3入力NANDゲート)からなり、桁選択回路からの桁選択信号とHandshake2からの信号を用いてデータを書き込むデコーダのラッチ機能をOFFし、データが書き込まれた後ラッチ機能をONさせる。つぎに、データ処理回路であるが、これは、MC14 513Bからなり、BCDコードで入力されたデータを7Seg.-Led.用の信号7ビット(a~f)に変換する。また、データをラッチする機能を持つ。

- ・Green,Red-Led.ON/OFF回路

- この回路は、74LS06(インバータ(オープンコレクタ))からなり、CPUボードから送られてくるそれぞれのLed.のON/OFF信号を反転させ てフロントボードのLed.へ送る機能を持つ。

- ・4ビットディップスイッチ信号処理回路

- この回路は、74LS04(NOTゲート)からなり、フロントボードでの4ビットディップスイッチのスイッチングに対応した信号をCPUボードへ送る機能を持つ。

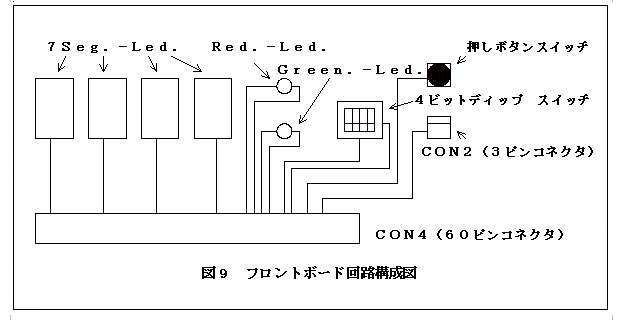

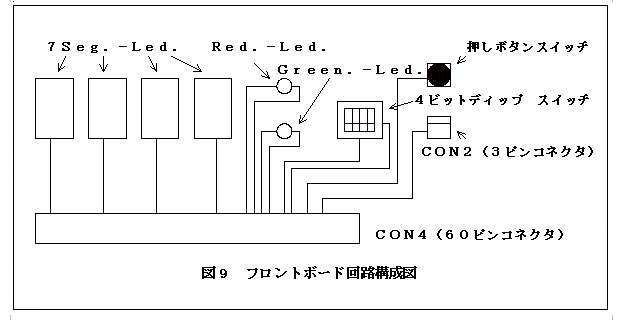

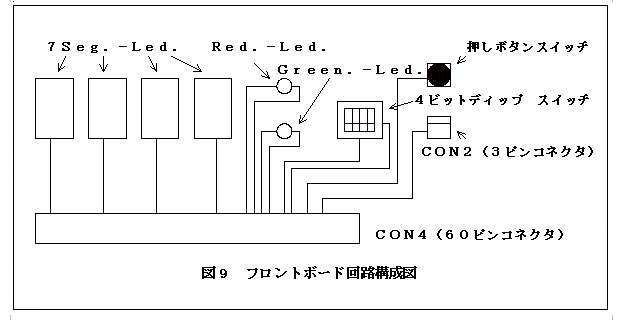

フロントボード

フロントボードの回路構成図を図9に示す。ここでは、フロントボードの各回路について説明する。

- ・7Seg.-Led.回路

- メインボードのデータラッチON/OFF及びデータ処理回路から出力されたデータ信号は、メインボードとフロントボードをつなぐケーブルを通り7Seg.-Led.の対応するピンに入力される。

- ・Green,Red-Led.回路

- メインボードのGreen,Red-Led.ON/OFF回路から送られてくる各Led.のON/OFF信号は、メインボードとフロントボードをつなぐケーブルを通り各Led.に入力される。

- ・4ビットディップスイッチ回路

- 4ビットディップスイッチにより入力されたON/OFF信号は、メインボードとフロントボードをつなぐケーブルを通り、4ビットディップスイッチ信号処理回路に送られる。

- ・押しボタンスイッチ回路

- 押しボタンスイッチにより入力された信号は、メインボードとフロントボードをつなぐケーブルを通り、チャタリング防止回路に送られる。

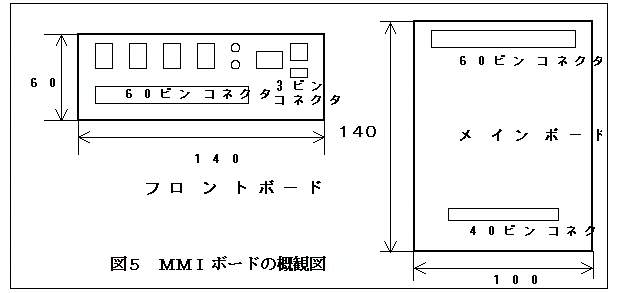

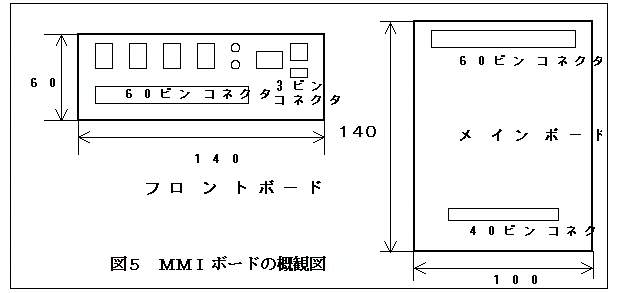

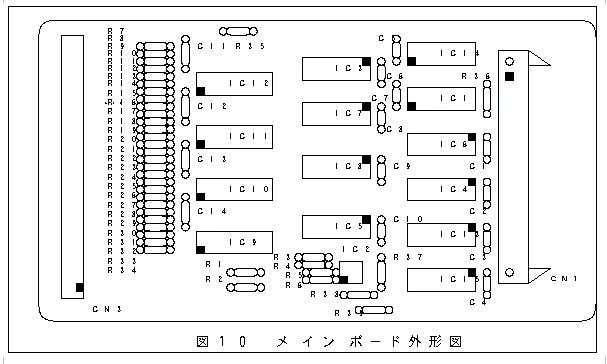

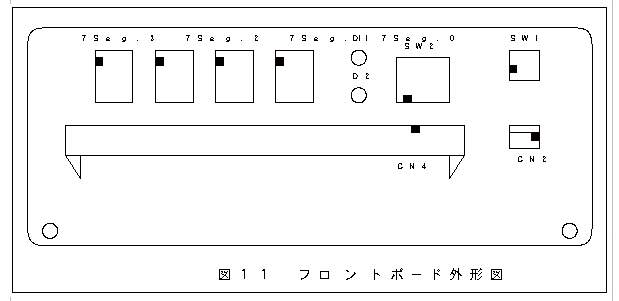

- ボード仕様

- 130 rMMIボードは、メインボードとフロントボードに分かれている。メインボードの大きさは、VMEラックに収納する事を考慮に入れて決定した。その大きさは、100mm×140mmである。フロントボードの大きさは、VMEラックの側面に取り付ける事を考慮に入れて決定した。その大きさは、60mm×140mmである。

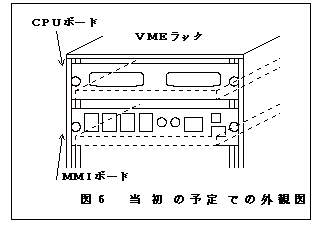

今回、図4の外観図に示したように、MMIボードをフロントボードとメインボードに分けた。

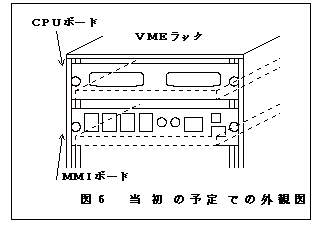

メインボードとCPUボードは、40ピンコネクタとケーブルで接続する。当初の予定では、図6の外観図のように両ボードを接続してVMEラック内に格納するはずであった。しかし、フロントボードの大きさの制約があり、7Seg.-Led.の小型のタイプが入手できない事がわかったために、ボードを分離してメインボードとフロントボードを60ピンのコネクタとケーブルで接続する事となった。

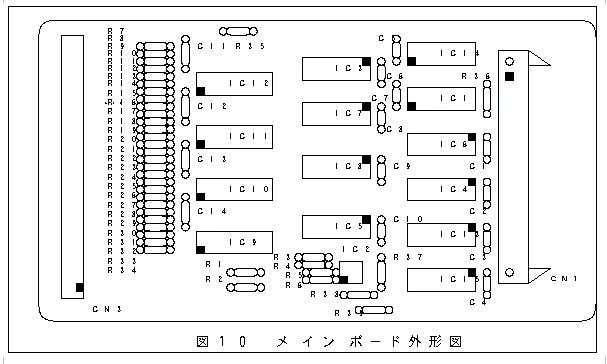

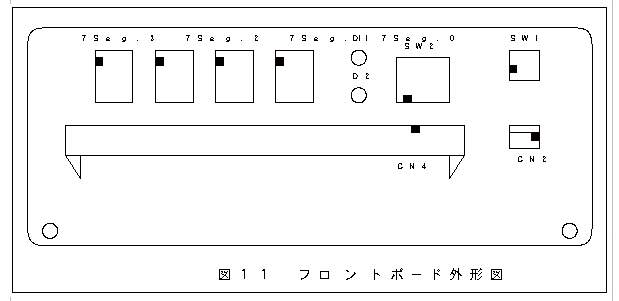

以下に、メインボードとフロントボードの外形図を示す。

・メインボード

・フロントボード

- インターフェイス仕様

- 以下に、各コネクタのピンアサインを示す。

CON1

| ピン番号 | 方向※ | 内容 | ピン番号 | 方向※ | 内容 |

| 1 | ← | Vcc | 21 | - | GND |

| 2 | → | Hadshake 1 | 22(PB0) | → | 4ビットディップスイッチON/OFF(0) |

| 3 | 未使用 | TIN | 23 | - | GND |

| 4 | ← | Handshake 2 ※※ | 24(PB1) | → | 4ビットディップスイッチON/OFF(1) |

| 5 | ← | TOUT | 25 | - | GND |

| 6(PA0) | ← | 7Seg.-Led.data(0) | 26(PB2) | → | 4ビットディップスイッチON/OFF(2) |

| 7 | - | GND | 27 | - | GND |

| 8(PA1) | ← | 7Seg.-Led.data(1) | 28(PB3) | → | 4ビットディップスイッチON/OFF(3) |

| 9 | - | GND | 29 | - | GND |

| 10(PA2) | ← | 7Seg.-Led.data(2) | 30(PB4) | ← | テスト信号入力 |

| 11 | - | GND | 31 | - | GND |

| 12(PA3) | ← | 7Seg.-Led.data(3) | 32(PB5) | → | テスト信号出力 |

| 13 | - | GND | 33 | - | GND |

| 14(PA4) | ← | 7Seg.-Led.選択(下位) | 34(PB6) | ← | 勝敗判定装置ON/OFF信号 |

| 15 | - | GND | 35 | - | GND |

| 16(PA5) | ← | 7Seg.-Led.選択(上位) | 36(PB7) | 未使用 | 未使用 |

| 17 | - | GND | 37 | - | GND |

| 18(PA6) | ← | Red-Led.ON/OFF | 38 | 未使用 | Handshake 3 |

| 19 | - | GND | 39 | ← | GND |

| 20(PA7) | ← | Green-Led.ON/OFF | 40 | → | Handshake 4 ※※※ |

※ 方向は、”←”CPUボードからメインボードへの入力

”→”メインボードからCPUボードへの出力を表す。

※※ Handshake 2の信号は、デコーダのデータラッチのタイミング用である。

※※※ Handshake 4の信号は、押しボタンスイッチのON/OFF信号である。

CON2

| 番号 | 方向※ | 内容 |

| 1 | 未使用 | 未使用 |

| 2 | ← | 勝敗判定装置ON/OFF信号 |

| 3 | → | 勝敗判定装置ON/OFF信号(折り返し) |

※ 方向は、”←”勝敗判定装置からフロントボードへの入力

”→”フロントボードから勝敗判定装置への出力を表す。

CON3(CON4)

| 番号 | 方向※ | 内容 | 番号 | 方向※ | 内容 |

| 1 | 未使用 | 未使用 | 31 | 未使用 | 未使用 |

| 2 | 未使用 | 未使用 | 32 | 未使用 | 未使用 |

| 3 | 未使用 | 未使用 | 33 | - | GND |

| 4 | ← | 押しボタンスイッチon/off信号 | 34 | → | 7Seg.-Led.1信号(a) |

| 5 | ← | 押しボタンスイッチon/off信号 | 35 | → | 7Seg.-Led.1信号(g) |

| 6 | - | GND | 36 | → | 7Seg.-Led.1信号(f) |

| 7 | 未使用 | 未使用 | 37 | → | 7Seg.-Led.1信号(b) |

| 8 | 未使用 | 未使用 | 38 | → | 7Seg.-Led.1信号(c) |

| 9 | ← | 3\3ピンコネクタ(3) | 39 | → | 7Seg.-Led.1信号(d) |

| 10 | ← | 3ピンコネクタ(2) | 40 | → | |

| 11 | 未使用 | 未使用 | 41 | 未使用 | 未使用 |

| 12 | - | GND | 42 | 未使用 | 未使用 |

| 13 | ← | 4ビットディップスイッチON/OFF(3) | 43 | - | GND |

| 14 | ← | 4ビットディップスイッチON/OFF(2) | 44 | → | 7Seg.-Led.2信号(a) |

| 15 | ← | 4ビットディップスイッチON/OFF(1) | 45 | → | 7Seg.-Led.2信号(g) |

| 16 | ← | 4ビットディップスイッチON/OFF(0) | 46 | → | 7Seg.-Led.2信号(f) |

| 17 | - | Vcc | 47 | → | 7Seg.-Led.2信号(b) |

| 18 | → | Green-Led.ON/OFF信号 | 48 | → | 7Seg.-Led.2信号(c) |

| 19 | - | Vcc | 49 | → | 7Seg.-Led.2信号(d) |

| 20 | → | Red-Led.ON/OFF信号 | 50 | → | 7Seg.-Led.2信号(e) |

| 21 | 未使用 | 未使用 | 51 | 未使用 | 未使用 |

| 22 | 未使用 | 未使用 | 52 | 未使用 | 未使用 |

| 23 | - | GND | 53 | - | GND |

| 24 | → | 7Seg.-Led. 0信号(a) | 54 | → | 7Seg.-Led.3信号(a) |

| 25 | → | 7Seg.-Led. 0信号(f) | 55 | → | 7Seg.-Led.3信号(g) |

| 26 | → | 7Seg.-Led. 0信号(f) | 56 | → | 7Seg.-Led.3信号(f) |

| 27 | → | 7Seg.-Led. 0信号(b) | 57 | → | 7Seg.-Led.3信号(b) |

| 28 | → | 7Seg.-Led. 0信号(c) | 58 | → | 7Seg.-Led.3信号(c) |

| 29 | → | 7Seg.-Led. 0信号(d) | 59 | → | 7Seg.-Led.3信号(d) |

| 30 | → | 7Seg.-Led. 0信号(e) | 60 | → | 7Seg.-Led.3信号(e) |

※ 方向は、”←”フロントボードからメインボードへの入力

”→”メインボードからフロントボードへの出力を表す。