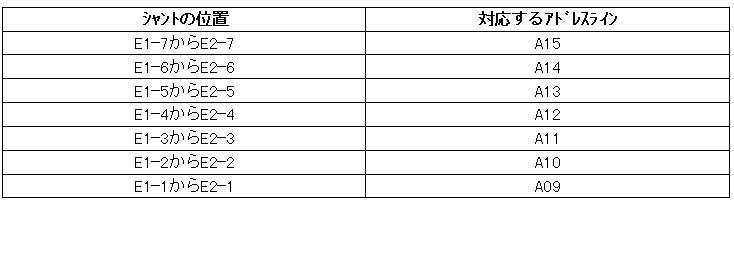

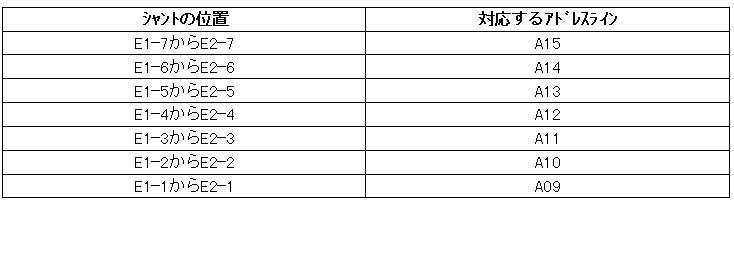

�@�@�@�@�@�@�@�@�@�@�@�}1�@�h�^�n�A�h���X�V�����g����U��

�@�@I/O���ް����ڽ�̼��ẮA����g�����Ԃł���AVIPC310�ɂ������ذ�ް����ڽ�̑I�����ł���B

�Ⴆ�AI/O���ް����ڽ��$6000(A16��Ԓ�)�Ƃ���Ȃ�A��ذ�ް����ڽ�́A$600000(A24��Ԓ�)�ƂȂ�B�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@

�l�o�t�{�[�h

�@�͂��߂ɁA�l�o�t�{�[�h�͂b�o�t�{�[�h�Ƃh�^�n�{�[�h�̂Q���ō\������Ă���B

�b�o�t�{�[�h�i���́@�u�r�a�b�[�P�j�ɂ͂q�r�Q�R�Q�b�Ƃ䂤�R�l�N�^���Q���ڂ��Ă��āA����ŊO���Ƃ̃f�[�^������肷�邱�Ƃ��ł���B

�h�^�n�{�[�h�i���́@�u�h�o�b�R�P�O�j�̓��[�^���[�G���R�[�_�{�[�h��IP-Digital�S�W�{�[�h�𓋍ڂ��Ă���BIP-Digital�S�W�{�[�h�ɂ�MC68230 PARALLEL INTERFACE/TIMER(PI/T)�i�T�O�s���̃R�l�N�^�j�𓋍ڂ��Ă��āA����ŊO���Ƃ̃f�[�^������肷��B

�@���̂��߁A�����ł͂b�o�t�{�[�h�Ƃh�^�n�{�[�h�Ƃɕ����ĉ�����Ă����B

�i�P�j�l�o�t�{�[�h�̋@�\���

�m�P�n�b�o�t�{�[�h�̋@�\���

�@����

�@���g���[����MPU 68000�́A���ʂȓ��o�͖��߂��������AI/O���������[��ԁ@�@

�ɔz�u���郁�����[�E�}�b�v�g�������̗p���Ă���B��ɂP�U�l�o�C�g�̃����@�@

���[��Ԃ���l�ɃA�N�Z�X���邱�Ƃ��ł���B68000�ł́A���CLK���͂̂P�O�@�@

�N���b�N����E�M�������I�ɏo�͂��Ă���B�ʏ�68000�̃f�[�^���o�� �́AE�@�@

�M���ƊW�Ȃ����ɍs���Ă���B68000�͂P�U�r�b�g�b�o�t�ł���Ȃ���@�@

�������W�X�^�́A���ׂĂR�Q�r�b�g�ɂȂ��Ă���B���A���W�X�^�͗p�r�Ɋւ��@�@

�Ă��܂萧���̏��Ȃ��ėp���W�X�^�������̗p���Ă���̂ŁA���W�X�^�Ԃ́@�@�@

�f�[�^�]���Ȃǂ̉����炷���Ƃ��ł���B

�A���W�X�^

�@68000�̃��W�X�^�́A�f�[�^���W�X�^ Dn(n:0�`7)�A�A�h���X���W�X�^ An(n:0�@�@

�`7)�A�X�e�[�^�X���W�X�^�r�q�A�v���O�����J�E���^�o�b������B�f�[�^���W�@�@

�X�^�E�A�h���X���W�X�^�̂����p�r�����܂��Ă���̂́A�X�[�p�o�C�U�p�X�@�@�@

�^�b�N�|�C���^�i�r�r�o�j�ƃ��[�U�p�X�^�b�N�|�C���^�i�t�r�o�j�̂Q�{�����@�@

�Ō�́A�ėp���W�X�^�Ƃ��Ďg�����Ƃ��ł���B�r�r�o�E�t�r�o����A7���蓖�@�@

�Ă��Ă��āA�ǂ�����g�����͂r�q�̓��e�i�r�r�b�g�j�ɂ���Č��܂�B

�B�X�[�p�o�C�U�X�e�[�g�ƃ��[�U�X�e�[�g

�@68000�́A�V�X�e���v���O�����������Ǘ��Ȃǂ̑�������邱�Ƃ��ł���悤�@�@

�ɁA���s���̏�Ԃ��X�[�p�o�C�U�X�e�[�g�ƃ��[�U�X�e�[�g�ɕ����āA����@�@

�̖��߂́A�X�[�p�o�C�U�X�e�[�g�ł������s�ł��Ȃ��悤�ɂ��Ă���B�����@�@

�̖��߂́A�������߂ƌĂ�r�q�̕ύX�⊄�荞�ݏ����Ɋւ��閽�ߌS������@�@

�ɑ�����B

�C68000��������f�[�^�^

�@68000�́A�P�A�S�A�W�A�P�U�A�R�Q�r�b�g���̃f�[�^����舵�����Ƃ��ł���B

�����̓��e�Ƃ��ẮA�r�b�g�f�[�^�A��i���\�i���A�o�C�g�f�[�^�A���[�h�f�[�^�A

�����O�o�C�g�f�[�^�������Ƃ��ł���B�f�[�^���W�X�^�́A�S��ނ̃f�[�^��ێ�

���邱�Ƃ��ł��邪�A�A�h���X���W�X�^�́A�P�U�r�b�g�A�R�Q�r�b�g��P�ʂƂ��Ĉ����B

�D��O����

�@��O����VECTOR�́A�b�o�t����O�������[�`���̃A�h���X��ׂɂO�`�@�@�@

�Q�T�T�Ԃ܂ł̂Q�T�U��ނ��p�ӂ���A�O�Ԓn����R�e�e�Ԓn�܂ł̂P�j�o

�C�g�ɔz�u����Ă���B���̂��ߕK�v�Ƃ��鉞������O�����v���O�����̐�@�@�@

���Ԓn��VECTOR TABLE�ɏ�������ł����Ȃ���Ȃ�Ȃ��B

�E�o�X�C���^�[�t�F�C�X�@�\

�@�U�W�O�O�O�̃o�X�C���^�[�t�F�C�X�̑傫�ȓ����́A�����C���^�[�@�@�@�@

�t�F�C�X�ł���B���̔����C���^�[�t�F�C�X�́A�o�X�N���b�N�������ȁ@�@�@

���B���̂����o�X�T�C�N���̏I���͂h�^�n������̉����M���i�c�s�`�b�j�@�@�@

�o�[�A�c�������@�s���������������@�`���������������������j�ɂ���čs�@�@�@

����B���̕����͑����̉�H�̑���͂�����̂́A�V�X�e���̗Z�ʐ������@�@�@

���̂ŁA�P�U�r�b�g�V�X�e���Ƃ��Ă͓K�Ȃ��̂ł���B�U�W�O�O�O�́A�X�@�@�@

�ɓ������C���^�[�t�F�C�X���[�h�ɐ�ւ��ď]�������J������Ă���B�@�@�@

�W�r�b�g���ӂk�r�h�����ڑ��ł���B�W�r�b�g���ӂk�r�h�͂P�U�r�b�g�V�X�@�@�@

�e���ɂ����Ă��d�v�Ȃh�^�n�@���ڑ��\�ɂ���B

�F �U�W�O�O�O�l�o�t�̒[�q�@�\

�P�D�A�h���X�o�X�i�`�P�`�`�Q�R�j

�@�@�`�P�`�`�Q�R�̂Q�R�{�̃A�h���X�o�X������B�[�q�Ƃ��Ă͂Q�R�{���邪�A�@�@

��q�̂t�c�r�o�[�C�k�c�r�o�[�̐M�����ƍ��킹�ĂQ�S�r�b�g�̃A�h���X�M�@�@�@

���ɂ��P�U�l�o�C�g�̃�������Ԃ��A�N�Z�X���邱�Ƃ��ł���B�P�U�i�\�@�@�@

���Ł��O�O�O�O�O�O�Ԓn���灐�e�e�e�e�e�e�Ԓn�ƂȂ�B

�Q�D�f�[�^�o�X�i�c�P�`�c�P�T�j

�@�@�P�U�r�b�g�̑o�������o�X�ň�x�ɂP�U�r�b�g�̃f�[�^��]�����邱�Ƃ��@�@�@

�ł���B�ꍇ�ɂ���Ă͏�ʂW�r�b�g�i�c�W�`�c�P�T�j�������g������A���@�@�@

�ʂW�r�b�g�i�c�O�`�c�V�j�������g�����Ƃ��ł���B�R�Q�r�b�g�̃f�[�^�]�@�@�@

���͂P�U�r�b�g���Q��ɕ����čs����B�U�W�O�O�O�ł͂R�Q�r�b�g�f�[�@�@�@

�^�������O���[�h�A�P�U�r�b�g�f�[�^�����[�h�A�W�r�b�g�f�[�^���o�C�g�Ɓ@�@�@

�Ă�ł���B

�R�D������M���i�`�r�o�[�C�q�^�v�o�[�C�t�c�r�o�[�C�k�c�r�o�[�C�c�s�`�b�j�o�[�j

�@�@�������Ƃ̐ڑ���f�[�^�]���ɂ����čł���{�I�ȐM���ł���A�c�s�`�b�j�@�@

�o�[�������M���͓������̃f�[�^�]���ɂ��g����B

�@�@�`�r�o�[�i�`�����������@�r�����������j�̓A�h���X�o�X��ɗL���ȃA�h���X�@

���m�肵�Ă��邱�Ƃ������A�����ɂl�o�t���������i���邢�͎��ӂk�r�h�j���A�@

�N�Z�X���Ă��邱�Ƃ������Ă���B

�@�@�q�^�v�o�[�i�q�������^�v���������j�̓f�[�^�]���̕����������Ă���A�g�Ł@

���[�h�A�k�Ń��C�g�ł���B

�@�@�t�c�r�o�[�C�k�c�r�o�[�i�t���������@�c�������@�r�����������C�k���������@

�c������ �r�����������j�̓f�[�^�]�������[�h�T�C�Y�ōs�����A�o�C�g�T�C�Y�Ł@

�s�����������B�t�c�r�o�[�͏�ʂW�r�b�g�A�k�c�r�o�[�͉��ʂW�r�b�g�ɑΉ����@

�Ă���B�����̐M�����A�T�[�g�������[�h�f�[�^�A�t�c�r�o�[�Ƃk�c�r�o�[�@

���P�ƂŃA�T�[�g�������ꂼ���ʂW�r�b�g�̂݁A���ʂW�r�b�g�݂̂Ƃ̂�B

�@�c�s�`�b�j�o�[�i�c������ �s�������������� �`���������������������j�͔�@

�����o�X���\��������I�M���ł���B�l�o�t�͂��̐M�����O��������͂����@

�܂Ńf�[�^�]���̃T�C�N�����I�����Ȃ��B�c�s�`�b�j�o�[���������͂����@�@

���[�h�^���C�g�̃T�C�N���͑����I���A�x����Βx���I���B�܂�O���f�o�@

�C�X�i����������ӂk�r�h�j�̃X�s�[�h�ɉ����đ������x�������R�ɒ��߂ł����@

�̂悢�f�o�C�X���\�����邱�Ƃ��\�ɂȂ�B�v�҂͂����̂��Ƃ��l�����ā@

�c�s�`�b�j�o�[�����̉�H���쐬���Ȃ���Ȃ�Ȃ��B

�S�D�U�W�O�O�O���Ӑ���M���i�d�C�u�l�`�o�[�C�u�o�`�o�[�j

�@ �U�W�O�O�O�l�o�t���g�����V�X�e���ɁA�]���̂W�r�b�g�l�o�t�i�U�W�O�O��U�@

�W�O�X�j�Ŏg���Ă������ӂk�r�h��ڑ����邽�߂̒[�q�ł���B�W�r�b�g�l�o�t�@

�p�̎��ӂk�r�h�͓������f�[�^�]�����s���Ă���B���̂��߂d�C�u�l�`�o�[�C�u�@

�o�`�o�[���g���ē������f�[�^�]�����ł���悤�ɂȂ��Ă���B

�@�d�i�d�����������j�͓������f�[�^�]���ɂ�����N���b�N�Ƃ��ē����A�d�̗��@

������ɓ������ăf�[�^�]�����s����B�U�W�O�O�̃N���b�N���Q�M���A�U�W�O�X�̂d�M���ɑ�������B

�@�u�l�`�o�[�i�u�������� �l���������� �`�����������j�͂U�W�O�O�O�������@

���Ńf�[�^�]�������Ă��邱�Ƃ������M���ŁA���ӂk�r�h�͂u�l�`�o�[���A�T�[�@

�g����Ă�����Ԃ̂d�̗���������g��Ȃ���Ȃ�Ȃ��B�U�W�O�O�̂u�l�`�ɑ�������M���ł���B

�@�u�o�`�o�[�i�u�������� �o������������������ �`�����������j�͂l�o�t�Ɂ@

���ē������f�[�^�]����v������M���ł���B���������ē������f�[�^�]�����@

�K�v�ȃf�o�C�X���A�N�Z�X���ꂽ�Ƃ��A�u�o�`�o�[���A�T�[�g���Ă��悢�B�@

�l�o�t�̓���������ӂk�r�h���A�N�Z�X�����Ƃ��ɂ́A���̃f�[�^���������ł��@

�邩�����ł��邩�͂킩��Ȃ��B�c�s�`�b�j�o�[�����͂����Δ����ł���A

�u�o�`�o�[�����͂����Γ������ł���B

�T�D���荞�ݓ��͒[�q�i�h�o�k�O�o�[�`�h�o�k�Q�o�[�j

�@ �U�W�O�O�O�͗D�揇�ʂ̂������̊��荞�݁i���x���P�`���x���V�j���g���@

���Ƃ��ł���B�D��x�̓��x���P�������Ƃ��Ⴍ���x���V�������Ƃ������B�܂��@

���x���V�͂m�l�h�i�m���� �l�������������� �h�����������������j�Ƃ��ē����B

�h�o�k�O�o�[�`�h�o�k�Q�o�[�̂R�{���g���āi�O�O�O�j�Q�`�i�P�P�P�j�Q�Ɂ@

�R�[�h���������荞�ݐM������͂���B�i�O�O�O�j�Q�͊��荞�ݗv���̂Ȃ���Ԃł���B�@

�U�D�o�X�A�[�r�g���[�V��������i�a�q�o�[�A�a�f�o�[�A�a�f�`�b�j�o�[�j

�@�o�X�A�[�r�g���[�V�����Ƃ̓o�X�̔z���ł���A�l�o�t�ȊO�Ƀo�X���g���f�o�C�X������ꍇ

�o�X���g�������i�o�X�}�X�^���j�̂��Ƃ�����邽�߂̐M���ł���B

�@ �a�q�o�[�i�a���� �q�������������j�͂l�o�t�ȊO�̃f�o�C�X���l�o�t�ɑ�

�ăo�X�}�X�^����v������M���ł���B

�@ �a�f�o�[�i�a���� �f���������j�͂a�q�o�[�ɑ���Ή��M���ł���A�l�o�t�@

�͎��̃o�X�T�C�N���Ńo�X�}�X�^�����������B�i�܂�O���f�o�C�X���o�X�}�@

�X�^�Ƃ��ăo�X���g����j���Ƃ��Ӗ�����B

�@ �a�f�`�b�j�o�[�͂a�f�o�[�����O���f�o�C�X�����݃o�X�}�X�^�Ƃ��ăo�X�@

���L���Ă��邱�Ƃ��l�o�t�Ƒ��̊O���f�o�C�X�ɒm�点��M���ł���B�����@

�R�{�̐���M�����g�����Ƃɂ������̂悢�o�X�}�X�^���̎�n�����s����B

�V�D�v���Z�b�T�X�e�[�^�X�i�e�b�O�`�e�b�Q�j

�@�l�o�t���ǂ̂悤�ȏ�Ԃœ��삵�Ă���̂���m�点��M���ł���B�X�[�p�o�@

�C�U��Ԃ����[�U��Ԃ��A�f�[�^�̃A�N�Z�X�����߂̃t�F�`���A�܂����荞�ݐM�@

������t������ԓ����R�r�b�g�ɃR�[�h�����ďo�͂��Ă���B

�W�D�V�X�e���R���g���[���i�a�d�q�q�o�[�C�q�d�r�o�[�C�g�`�k�s�o�[�j

�@�a�d�q�q�o�[�i�a���� �d���������j�̓f�[�^�]���Ɉُ킪����l�o�t�ɒm��@

����M���ł���B�l�o�t�͂a�d�q�q�o�[���A�T�[�g�����ƌ��݂̃o�X�T�C�N���@

�𒆒f���A�o�X�G���[��O���������s����B

�@ �q�d�r�o�[�i�q���������j�͒ʏ�A���͒[�q�Ƃ��ē����V�X�e�����Z�b�g���s���B

�������q�d�r�d�s���߂����s�����Ƃ��͏o�͒[�q�Ƃ��ē������Z�b�g�[�q��

�ڑ����ꂽ�O���f�o�C�X�̃��Z�b�g���s���i�l�o�t�̓��Z�b�g����Ȃ��j�B

�@�g�`�k�s�o�[�i�g�������j�͒ʏ�A���͒[�q�Ƃ��ē����l�o�t�̃z�[���g�Ɏg�@

����B�g�`�k�s�o�[�M�����A�T�[�g�����Ƃl�o�t�͌��݂̃o�X�T�C�N�����I�@

����z�[���g�����B�z�[���g��Ԃł́A�A�h���X�o�X�A�f�[�^�o�X�̓X���[�X�@

�e�[�g��ԁA�q�^�v�o�[�C�`�r�o�[�C�t�c�r�o�[�C�k�c�r�o�[�́h�g�h�ɂȂ�B�@

�g�`�k�s�o�[�[�q���o�͂Ƃ��ē��삷��͓̂�d�o�X��Q�i�_�u���o�X�t�H�[���g�j

�����������Ƃ��ł���B��d�o�X��Q�Ƃ̓o�X�G���[�������ĂQ��N���邱�Ƃł���

�A�l�o�t�͎���z�[���g��Ԃɓ���A���Z�b�g�ȊO�ł͉ł��Ȃ��B

�X�D���̑��̐M���i�b�k�j�C�u�����C�u�����j

�@ �b�k�j�i�b���������j�͂l�o�t�����삷���{�ƂȂ�N���b�N��Ԃł���A

���̎����������Ă��Ȃ���Ȃ�Ȃ��B�܂������Ȃ�ꍇ�ɂ��~�܂��Ă͂Ȃ�Ȃ��B

�ō����g���̓o�[�W�����ɂ��U�D�O�C�W�D�O�C�P�Q�D�T�l�g���̂��̂�����B

������̃o�[�W�����ł��Œ���g���͂S�D�O�l�g���ł���B

�@�u�����i�d���j�A�u�����i�ݒu�j�͊e�Q�s������B����͂k�r�h�̃`�b�v���Ł@

�̓d�ʂ�����ɕۂ��߂ł���A�Q�s���Ƃ��ڑ����Ȃ���Ȃ�Ȃ��B

�i�Q�j�h�^�n�{�[�h�̋@�\���

�@�@VIPC310�̍\���`��

�@�@VIPC310�́A����@��I/O�\�������̎��IP�̈ꕔ�ł���BIP��ر�Ƃ��ā@�@�@

VIPC310�͋@�B�I�Ȏx���ƁA�d�C�I�Ȑڍ����A2�̼ݸ��ʲ�IP���A1�������ʲā@

IP�ɋ�������BVIPC310�̊O�ϐ}�́A���y�[�W�}1�ł���B

�@�@���߯�/����߯āA��A���荞�݂̓��������B�ް�ޏ�ł��ޯ�ذ�ɂ���ޯ��@���߂��\�ł���B

�@�@VIPC310�́A3U(�ݸ��ʲ�)�̗v�f�ɂ����VMEbus Specification C.1(IEEE�ɂ�@

��AP1014/D1.2�܂��́AIEC821bus�Ƃ��Ă��m���Ă���B)�ƌ�������BIP��ر�@�́A

DMA�ް�ނ�A68020�������u���悹���(6U(�����ʲ�)�ł���)�l�X�ȋ@�\�𗘗p�ł���B

IP��ر�́A���̕W���I��Industrybus�ł̗��p���ł���B

�@�@VIPC310�́AIP Logic�̐ڍ����@�ɏ]���BIP�݂͌��ɁAVIPC310�̑O�ʂ�ʂ��ā@

50��݂��ׯĹ���قɂ���Đڍ������B���IP�́A"A"�y��"B"�Ɩ��t�����Ă���B

���̪���̐ڍ��́A����@�ŁA����قłȂ��ꂽ���тł���AIP��ر����ިڸ��Y���t������B

�ڍ�����ك��́AVME�̼�������AVIPC310���@�����ɁA�������݁A�����������ł���B

IP��I/O����̐M���Ɉ˂炸�ɁAON/OFF���ł���B

�@�@�ǂ�ȂƂ��ł��AIP�́A��ذ��������ق̎w���킪�_�����Ă���AVMEbus����A

���������B��̕\���킪����A��ÂA���݂�IP�ɗp������B�ǂ̱����ɑ��Ă��A

�����̎w���m�ɂ���ׂɁA����͕����̊W�̂���LED��_��������(��O���̈�b��)�B

�@�@�ް�ޏ�������ޯ�́A�����������@�\�𗘗p����IP�ׂ̈��ޯ����ߗp�Ƃ��ėp������B

���A�ޯ�́AVMEbus+5�@���́ASTDBYײ݂���I�����Ďg�p�ł���B�@�ʏ�A�ޯ�̕⍲��p�́A

�è��RAM�ƁA�����v�Ɏg�p�����B

�@�@IP��I/O�́AVMEbusA16/D16��Ԓ��Ɉʒu����B�g�p�҂ƁA�Ǘ��҂̱����͋��ɁA�ǂݎ��A

�C���A��������(ý�/���)�̍�Ƃ���B���݂�IP��ɂ���I/O��Ԃ́AIP�̏ڍ��ɂ���āA

16�ޯĂ�ܰ�ނ�64�ƌ��߂��Ă���B���݂�IP���A64����L����PROM�̓��ڂ��ł���B�������āA���IP��A�y��B�́AShortI/O�@��Ԃ�VMEbus���т�64[KB]���A512�Ă��L����B

�@�@���荞�݂́A�S�ʓI�ɁA�w������B���݂�IP�́A��ɕ������ꂽ���荞�ݗv���ɂ��A

������s���BVIPC310�́AVMEbus��IRQ1,3,4,6�̎x��������B�����@�ݗv���������݂�IP�́A���g��8�ޯĂ�VECTOR���������Ȃ���Ȃ�Ȃ��B���@��VECTOR�́AVMEbus�Ɏ���m�点�黲�قŁA��������Ԃɋ��������B

�@�@VIPC310�́AVMEbusBERR�̑�����Ȃ��B��ij����́A�Ӗ��̖��������́A

���삵�Ă��Ȃ�CPU�ް�ޏ�̒�~��H��ɂ���āA��~�����B

�@�@��ܰ���ߤ��ܰ�ݤ�ؾ�Ċ��́A�S�ʓI�ɻ�߰Ă���Ă���B

�@�@VIPC310�́A5,12,-12�m���n�̓d����LC pį����ʂ��āA���݂�IP�ɋ�������B�@

����́A�������ި���ٍ�p�ƂƂ��ɁA��۸ނ̎g�p���\�ɂ��Ă���B

�@�AI/O���ڽ�̐ݒ�@

�@�@VIPC310���I/O�̱��ڽ�ݒ�@�́A��̗v�f�ɂ�茈�܂�B��́A�ް�ނ��ް����ڽ�ł���B��߂́A���߰��ɗv������鱸���ƁAIP�̵̾�Ăł��@��B�@�ް����ڽ�̐ݒ���@�́A�ȉ��Ő�������l�ɁA�l�̻��߰��ƁA����� �@�@�̵̾�Ăɂ���Č��߂���B

�@�@VIPC310�́AVMEbus��"Short I/O���́AA16/D16��Ԓ��ɁA512�Ă��߂�B �@

����́AIP��ԂƁA���݂�IP��I/O�Ԃ�16�ޯ�*64ܰ�ނ���Ȃ��Ă���B�ް�ނ��ް����ڽ�́A

���̼��ċy�сA�ެ��߰�ɂ���Đݒ肳���B������ۯ��z�u�̖͗l�́A�}�R�Ɏ�����Ă���B

�@�@���Ă͐ڍ������ƁA���ڽײ݂�"0"��^����B���Ă͊J�������ƁA���ڽײ݂�"1"��^����B

�Ⴆ�A7�̼��Ă̑S�Ă��ڍ����ꂽ���ɂ́A$0000�ƌ����ް����ڽ���n�������B

7�̼��Ă̑S�Ă��J�����ꂽ���ɂ́A$FE00�ƌ����ް����ڽ���n�������B���ڽײ݂ɑ��鼬�Ă̈ʒu�̊W�́A�}2�����ĂɎ�����ā@����B

�@�@I/O���ް����ڽ�̼��ẮA����g�����Ԃł���AVIPC310�ɂ������ذ�ް����ڽ�̑I�����ł���B

�Ⴆ�AI/O���ް����ڽ��$6000(A16��Ԓ�)�Ƃ���Ȃ�A��ذ�ް����ڽ�́A$600000(A24��Ԓ�)�ƂȂ�B

��葽���̏��邽�߂ɁA"��ذ�̱��ڽ�ݒ�@"�ƌ������ڂ��Q�Ƃ��Ă��������B

�@�@VIPC310�ł́A�����}3�Ɏ������l�ɁAI/O�ް����ڽ�ɁA$6000��Ă������̂����M�����B

�@�@VIPC310��VMEbus��Ԃ�A16���ɐ�߂�512�ẮA�l�̻��߰��ɕ��������(�}4�Q��)�B

�@�@���݂�IP�́A128��(&H$80��)��I/O��ԂɈ��16�ޯĂ̋�Ԃ�64���B�唼��IP�́A

۳���ް�̎����Ăł̂ݎg�p�����B������IP�ɂ���ăo�C�g�́A$1,$3���̵̾�Ă̈ʒu�𱸾�����B

����I/O�̊�Ă͕W���^��VMEbus��68000���̉��Z�������u�ŗ^������B�唼��IP�́A

I/O��ԂɊ��蓖�Ă�ꂽ�S�Ă��Ă��g�p���邱�Ƃ͂ł��Ȃ��B

�@�@���݂�IP�́A�g�p���Ă��Ȃ��Ă����ނ����邱�Ƃ��o����ꍇ������B

�g�p���Ă��Ȃ���Ԃւ̱��ڽ�w��́A��H�I��CPU���ѱ�Ă�N�Q���邱�Ƃ���

VMEbus BERR���N�������낤�B��������CPU�̋@�\���~�߂����Ȃ�A�g�p���Ă��@

�Ȃ���Ԃւ̱��ڽ�w������鎞��AIP�̋�Ԃɂɍ������܂Ȃ����AVMEbus��"�ݸ�"����B

�@�@�@�@�@�@�@�@�@�@�@�}1�@�h�^�n�A�h���X�V�����g����U��

�@�@I/O���ް����ڽ�̼��ẮA����g�����Ԃł���AVIPC310�ɂ������ذ�ް����ڽ�̑I�����ł���B

�Ⴆ�AI/O���ް����ڽ��$6000(A16��Ԓ�)�Ƃ���Ȃ�A��ذ�ް����ڽ�́A$600000(A24��Ԓ�)�ƂȂ�B�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@�@