PC/104 規格準拠 Cyclone III FPGA ボード

# **MS104-FPGA/C III**

## Hardware Manual

1 版

**ALPHA PROJECT**

<http://www.apnet.co.jp>

## ご使用になる前に

このたびは MS104-FPGA/CⅢをお買い上げいただき誠にありがとうございます。

本製品をお役立て頂くために、このマニュアルを十分お読みいただき、正しくお使い下さい。

今後共、弊社製品をご愛顧賜りますよう宜しくお願ひいたします。

## 梱包内容

本製品は、下記の品より構成されております。梱包内容をご確認のうえ、万が一、不足しているものがあればお買い上げの販売店までご連絡ください。

| MS-104-FPGA/CⅢ梱包内容 |     |         |

|--------------------|-----|---------|

| ●MS104-FPGA/CⅢ     | 1 枚 | ●CD-ROM |

| ●金属スペーサ            | 4 本 | ●ナット    |

| ●保証書               | 1 枚 | 4 個     |

■本製品の内容及び仕様は予告なしに変更されることがありますのでご了承ください。

## 取り扱い上の注意

- 本製品には、民生用の一般電子部品が使用されています。宇宙、航空、医療、原子力、運輸、交通、各種安全装置などで人命、事故に関わる特別な品質、信頼性が要求される用途でのご使用はご遠慮ください。

- 極端な高温下や低温下、または振動の激しい環境でのご使用はご遠慮ください。

- 水中、高湿度、油の多い環境でのご使用はご遠慮ください。

- 腐食性ガス、可燃性ガス等の環境中でのご使用はご遠慮ください。

- 基板の表面が水に濡れていれば、金属に接触した状態で電源を投入しないでください。

- 定格を越える電源を加えないでください。

- ノイズの多い環境での動作は保証しかねますのでご了承ください。

- 発煙や発火、異常な発熱があった場合には、すぐに電源を切ってください。

- 本書に記載される製品および技術のうち、「外国為替および外国貿易法」に定める規制貨物等（技術）に該当するものを輸出または国外に持ち出す場合には同法に基づく輸出許可が必要です。

- 本製品に付属するマニュアル、回路図の著作権は（株）アルファプロジェクトが保有しております。これらを無断で転用、掲載、譲渡、配布することは禁止します。

## 保証

- 本製品は万全の注意を払って製作されていますが、万一初期不良品であった場合、お買い上げ頂いた販売店へ保証書を添えてご返却ください。(弊社より直接お買い上げのお客様については、出荷時に全て登録済みとなっております。)

- 万が一、本製品を使用して事故または損失が発生した場合、弊社では一切その責を負いません。

- 保証内容、免責等につきましては、添付の保証書をご覧ください。

- 本製品を仕様範囲を越える条件において使用された場合については、動作は保証されません。

- 製品を改造した場合、保証は一切適用されません。

- 他社製品との接続互換性および相性問題は保証いたしません。

## 参考資料

本製品に付属している CD-ROM には、下記の参考資料が収録されておりますので、本マニュアルと合わせてご覧ください。

- Cyclone III Device Handbook ALTERA

- その他各社デバイスデータシート

## 参考 URL

下記の URL に本製品に関連するデバイスおよび規格の情報が掲載されておりますので、参考にしてください。

- ALTERA <http://www.altera.co.jp/>

## ソフトウェアについて

- 本製品には、ソフトウェアは付属しません。

本製品で動作するソフトウェアについては、「5. 関連製品のご案内」をご覧ください。

ソフトウェアに関するライセンス、保証、免責事項については、各製品のマニュアルをご覧ください。

## 目 次

|                            |    |

|----------------------------|----|

| <u>1. 概要</u>               | 1  |

| 1.1 製品概要 .....             | 1  |

| 1.2 機能及び特長 .....           | 1  |

| 1.3 仕様概要 .....             | 2  |

| 1.4 外形仕様 .....             | 3  |

| 1.5 回路構成 .....             | 4  |

| <u>2. 機能</u>               | 5  |

| 2.1 PC/104 バスの設定 .....     | 5  |

| 2.2 FPGA の設定 .....         | 5  |

| 2.3 FLASHROM .....         | 8  |

| 2.4 SDRAM .....            | 9  |

| 2.5 LED .....              | 10 |

| 2.6 クロック .....             | 11 |

| 2.7 操作スイッチ .....           | 12 |

| <u>3. 外部インタフェース</u>        | 14 |

| 3.1 PC/104 バス .....        | 14 |

| 3.2 拡張 I/O .....           | 18 |

| 3.3 シリアルインタフェース .....      | 23 |

| 3.4 JTAG インタフェース .....     | 23 |

| 3.5 電源 .....               | 24 |

| <u>4. テクニカルデータ</u>         | 26 |

| 4.1 外形寸法 .....             | 26 |

| 4.2 PC/104 ボードの接続 .....    | 27 |

| <u>5. 関連製品のご案内</u>         | 28 |

| 5.1 関連製品 .....             | 28 |

| <u>6. 製品サポートのご案内</u>       | 34 |

| <u>7. エンジニアリングサービスのご案内</u> | 35 |

# 1. 概要

## 1.1 製品概要

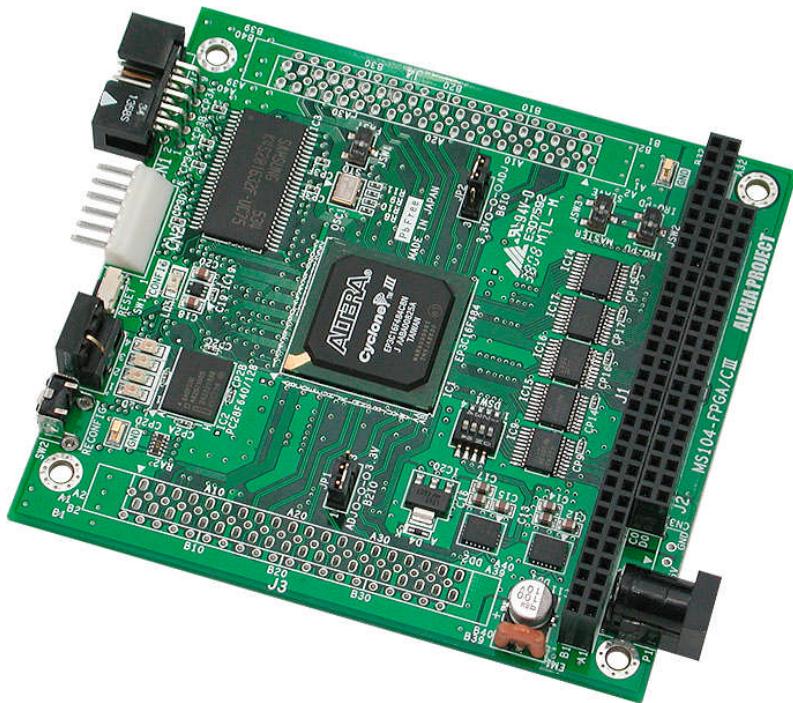

MS104-FPGA/C IIIは、ALTERA 社製 FPGA CycloneIII (EP3C16F484) を搭載した PC/104 規格準拠 FPGA ボードです。弊社製 PC/104 規格準拠 CPU ボード MS104-SH2、MS104-SH4、MS104-SH4AG または市販の PC/104 規格に準拠した CPU ボードに接続することで、画像処理、モータ制御、通信制御等、自由に機能を拡張することができます。

また、汎用 FPGA ボード及び Nios II プロセッサ搭載ボードとしてもお使いいただけます。

## 1.2 機能及び特長

### ■ FPGA CycloneIII EP3C16F484 搭載

<EP3C16F484 特長>

ロジックエレメント 15408 個

メモリ 504Kbit

マルチプライヤ 56 個

PLL 4 個

グローバルネットワーク 20 個

### ■ PC/104規格準拠

PC/104規格の弊社製ボードの他、各社のボードと接続することができます。

### ■ 大容量メモリ搭載

コンフィギュレーションメモリ、プログラムメモリとしてFLASHROM 8MByte、データメモリとしてSDRAM 16MByteを搭載しています。

### ■ 外部拡張が容易

ユーザ開放I/Oを112ピン(最大192ピン)コネクタに引き出しておりますので、接続が容易です。

### ■ サンプルHDLプログラムを提供

PC/104バスI/O空間、MEMORY空間のアクセスのためのサンプルHDLプログラムが提供されます。

### ■ 回路図を全て公開

回路図は全て公開されていますので、回路動作の確認やデバッグにお役立ていただけます。

\*1 PC/104 規格と一部異なる部分があります。詳しくは PC/104 バスの説明をご覧ください。

\*2 すべての PC/104 ボードとの互換性を保証するものではありません。

\*3 ソフトウェアは別途ご用意いただく必要があります。

### 1.3 仕様概要

MS104-FPGA/C III 仕様

| 機能                 | 仕様                                                                                                                                                    |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPGA               | Cyclone III EP3C16F484 (ALTERA 製)<br>ロジックエレメント 15408 個<br>メモリ 504Kbit<br>マルチプライヤ 56 個<br>PLL 4 個<br>グローバルネットワーク 20 個                                  |

|                    | サポートコンフィギュレーション<br>Intel アクティブパラレル x16 ファースト (AP ファースト POR)<br>Intel アクティブパラレル x16 (AP スタンダード POR)<br>JTAG                                            |

| クロック               | 水晶発振器 40MHz                                                                                                                                           |

| CONFIG/PROGRAM ROM | FLASHROM 8MByte<br>PC28F640P33 (numonyx (Intel) 製)                                                                                                    |

| SDRAM              | SDRAM 16MByte<br>K4S281632 (Samsung) または相当品                                                                                                           |

| I/O バス             | BANK1 3.3V I/O(J3) 16 本<br>BANK2 3.3/2.5/1.8/1.5/1.2V I/O(J3) 40 本<br>BANK5 3.3/2.5/1.8/1.5/1.2V I/O(J4) 16 本<br>BANK6 3.3 I/O(J4) 40 本<br>CLK 入力 4 本 |

| 外部拡張バス             | PC/104 規格準拠 (J1、J2)                                                                                                                                   |

| シリアル I/F           | 調歩同期式 1CH(CN2)                                                                                                                                        |

| JTAG I/F           | JTAG10 ピン (CN1)<br>ALTERA Byte-Blaster/USB-Baster 対応                                                                                                  |

| LED                | モニタ LED 4 個 (I/O ポートに接続)                                                                                                                              |

| 電源                 | DC5V±5%<br>(P1 または CN3 または J1、J2 から供給)                                                                                                                |

| 消費電流               | Typ 150 mA (弊社サンプルプログラム動作時)                                                                                                                           |

| 使用環境条件             | 温度 0°C~50°C (結露なし)                                                                                                                                    |

| 寸法                 | 90.2 × 95.9 mm (突起物を除く)                                                                                                                               |

Table 1.3-1 仕様概要

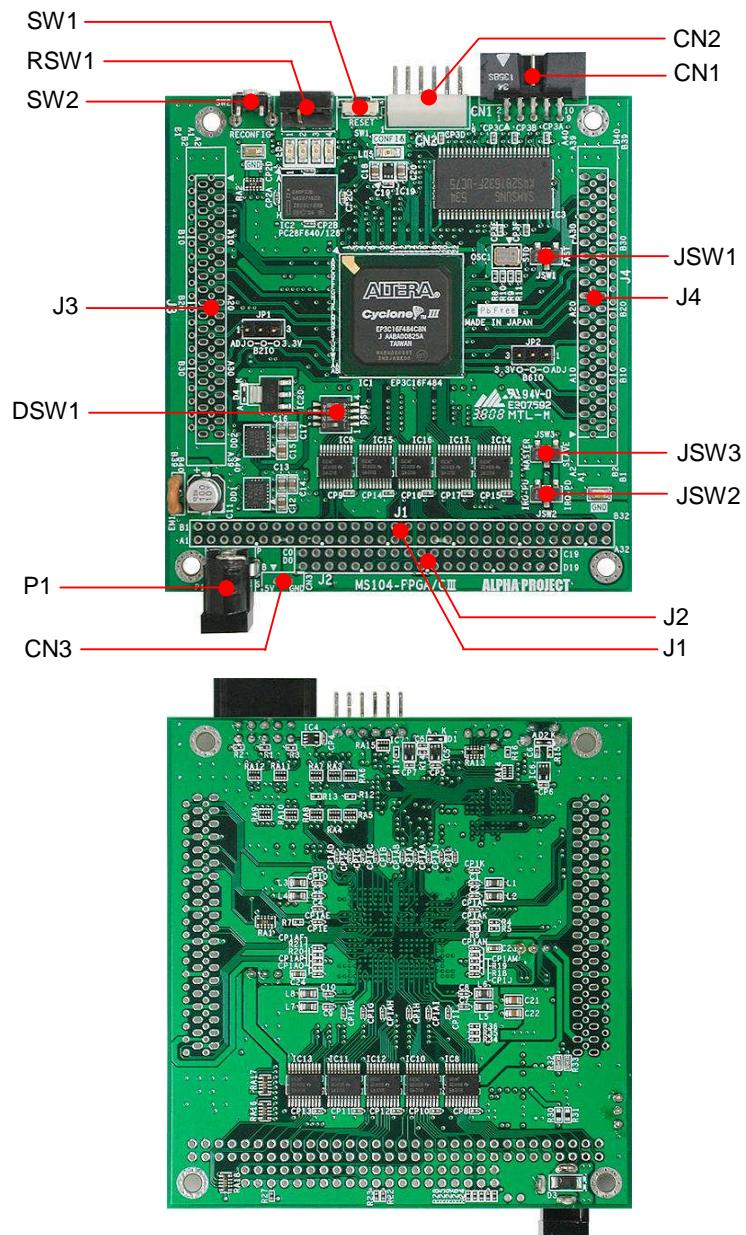

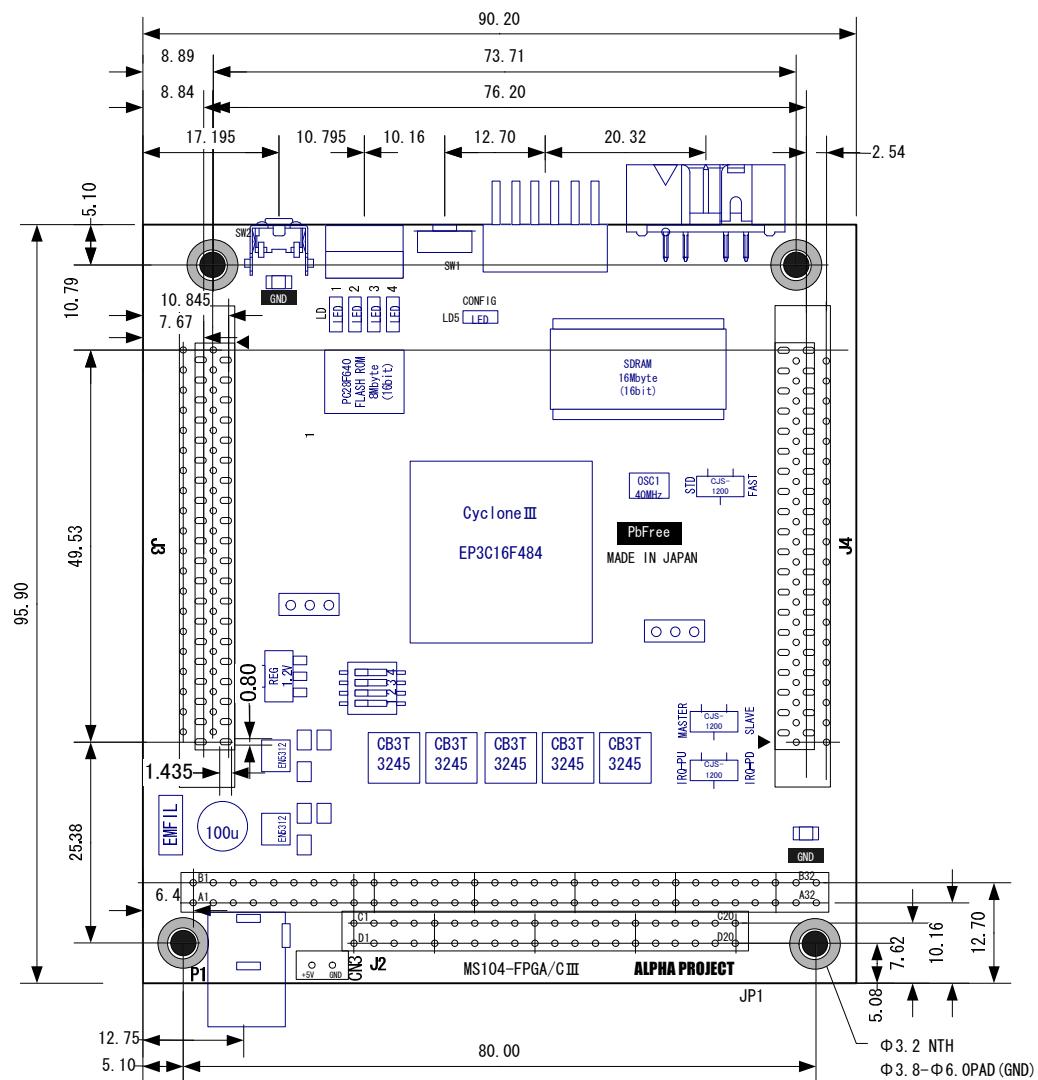

## 1.4 外形仕様

Fig 1.4-1 外形図

| コネクタ番号 | コネクタ型番/メーカー             | 用途            | 備考  |

|--------|-------------------------|---------------|-----|

| J1     | PC104-64HK              | PC/104 コネクタ   |     |

| J2     | PC104-40HK              | PC/104 コネクタ   |     |

| J3, J4 | FX2C-80S1.27DSA(71)/ヒロセ | I/O 拡張コネクタ    | 未実装 |

| CN1    | XG4C-1034/OMRON         | JTAG コネクタ     | 未実装 |

| CN2    | BS6P-SHF-1AA/日圧         | シリアル I/F コネクタ |     |

| CN3    | B2B-EH/日圧               | 電源コネクタ        | 未実装 |

| P1     | MJ-179/マル信無線電機          | DC ジャック       |     |

Table 1.4-1 コネクター一覧

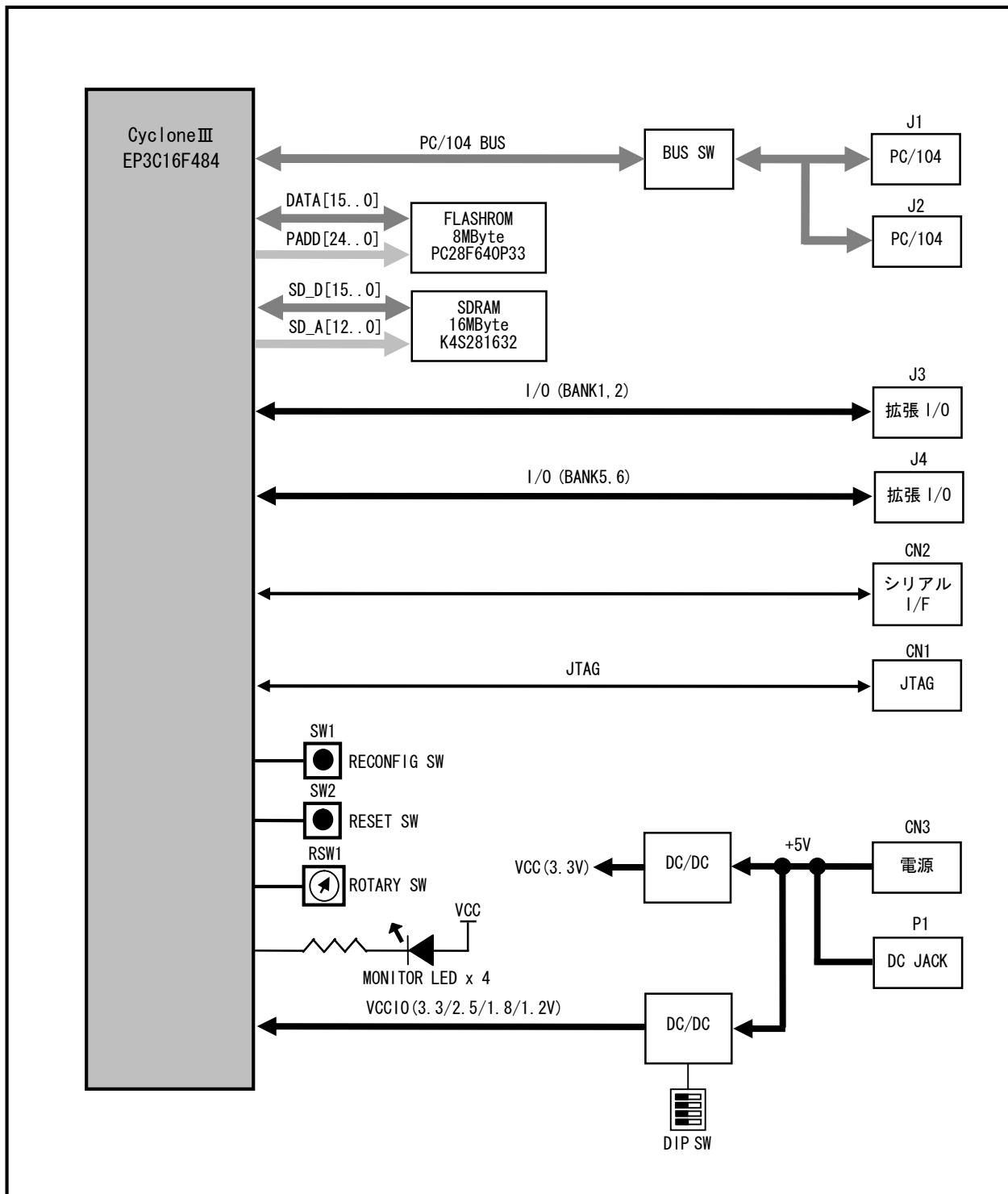

## 1.5 回路構成

## 2. 機能

### 2.1 PC/104 バスの設定

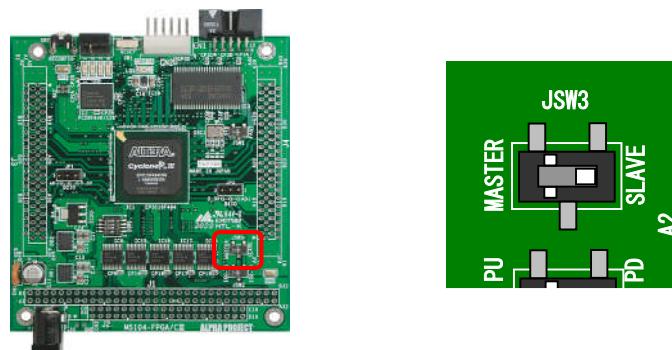

MS104-FPGA/C III のマスター/スレーブを JSW3 で設定することができます。MS104-FPGA/C III をマスターボードとして使用する場合は「MASTER」に、スレーブボードとして使用する場合は「SLAVE」に設定してください。

| JSW3   | PC/104 バス                             |

|--------|---------------------------------------|

| MASTER | MS104-FPGA/C III をマスターボードとして使用        |

| SLAVE  | MS104-FPGA/C III をスレーブボードとして使用(出荷時設定) |

Fig 2.1-1 PC/104 バスの設定

### 2.2 FPGA の設定

#### 2.2.1 コンフィギュレーション・モードの設定

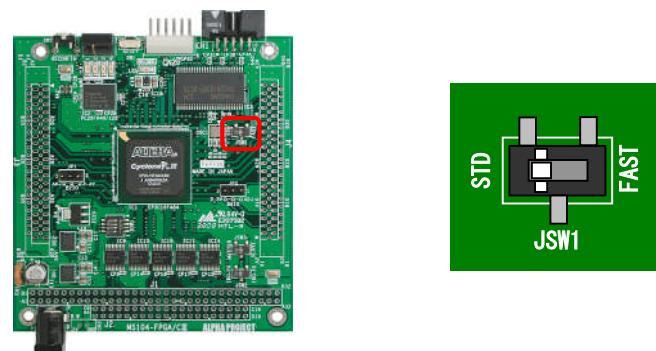

EP3C16F484 のコンフィギュレーション・モードは、JSW1 で設定することができます。

| JSW1 | コンフィギュレーション・モード              | パワーオンリセット時間 $T_{POR}$ (ms) |

|------|------------------------------|----------------------------|

| STD  | Intel アクティブ・パラレル x 16(出荷時設定) | $50 < T_{POR} < 200$       |

| FAST | Intel アクティブ・パラレル x 16 ファースト  | $3 < T_{POR} < 9$          |

Fig 2.2-1 コンフィギュレーション・モードの設定

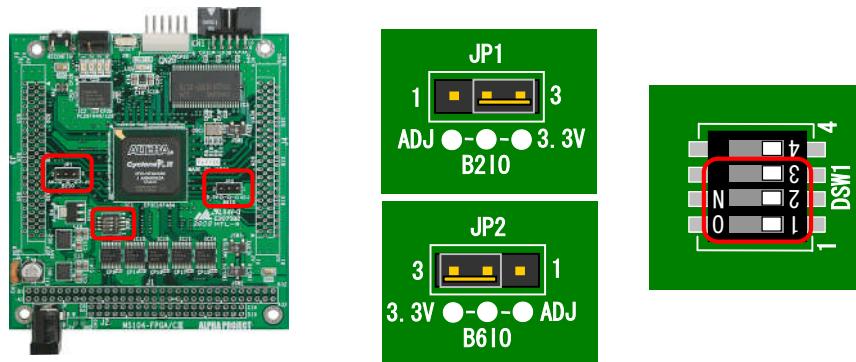

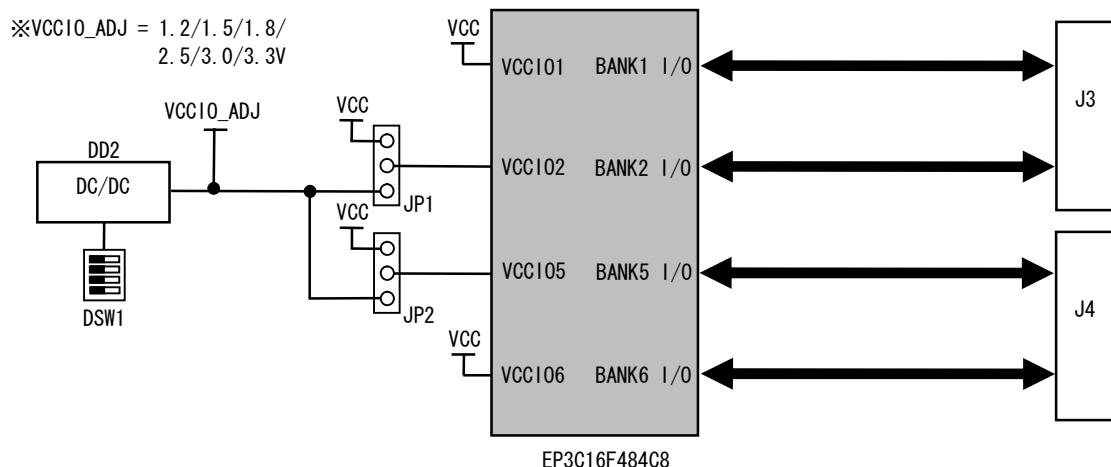

## 2.2.2 I/O BANK 電圧の設定

MS104-FPGA/C IIIでは、EP3C16F484 の I/O BANK2、5 の電圧を設定することができます。I/O BANK2.5 の電圧を JP1、JP2 で 3.3V/VCC\_ADJ どちらかに設定します。VCC\_ADJ に設定した場合、VCC\_ADJ 電圧を DSW1 で 1.2/1.5/1.8/2.5/3.0/3.3V いずれかの電圧に設定することができます。

| JP1           | I/O BANK2 電圧 |

|---------------|--------------|

| 1-2 短絡 (ADJ)  | VCCIO_ADJ    |

| 2-3 短絡 (3.3V) | 3.3V(出荷時設定)  |

| JP2           | I/O BANK6 電圧 |

|---------------|--------------|

| 1-2 短絡 (ADJ)  | VCCIO_ADJ    |

| 2-3 短絡 (3.3V) | 3.3V(出荷時設定)  |

| DSW1 |     |     | VCCIO_ADJ   |

|------|-----|-----|-------------|

| 1    | 2   | 3   |             |

| OFF  | OFF | OFF | 3.3V(出荷時設定) |

| OFF  | OFF | ON  | 2.5V        |

| OFF  | ON  | OFF | 1.8V        |

| OFF  | ON  | ON  | 1.5V        |

| ON   | OFF | OFF | 設定禁止        |

| ON   | OFF | ON  | 1.2V        |

| ON   | ON  | OFF | 設定禁止        |

| ON   | ON  | ON  | 3.0V        |

Fig 2.2-2 I/O BANK 電圧の設定

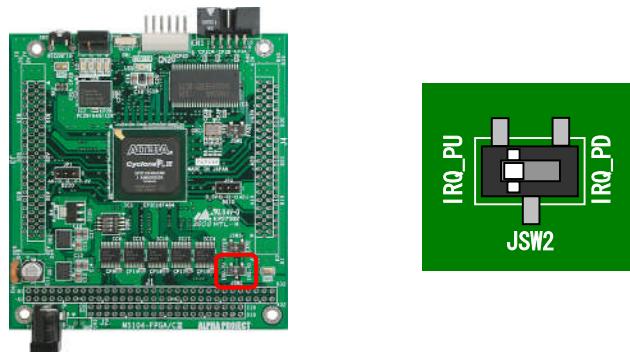

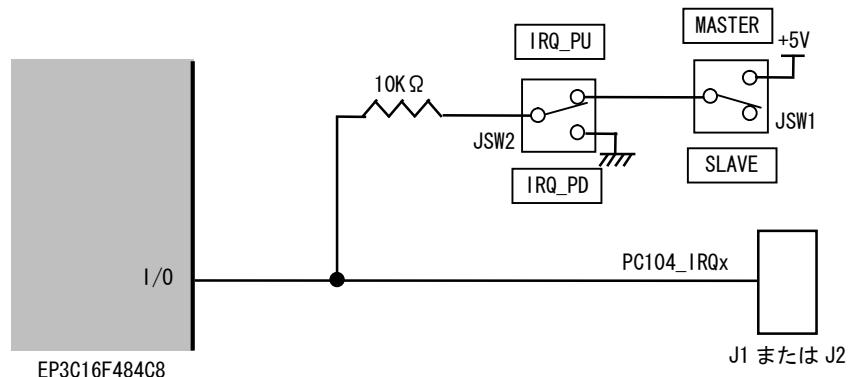

### 2.2.3 割り込み信号の設定

MS104-FPGA/C IIIでは割り込み信号(PC104\_IRQx)のプルアップ/プルダウンを JSW2 で設定します。ただし、本設定は本ボードをマスターボードとして使用する場合のみ有効になります。スレーブボードとして使用する場合はプルアップ側に固定して使用してください。この場合、割り込み信号にはプルアップ/プルダウンはされません。

| JSW2   | PC/104 バス                | 備考                   |

|--------|--------------------------|----------------------|

| IRQ_PU | PC104_IRQx をプルアップ(出荷時設定) | スレーブボードとして使用時はこちらに固定 |

| IRQ_PD | PC104_IRQx をプルダウン        |                      |

Fig 2.2-3 割り込み信号の設定

Fig 2.2-4 割り込み信号の回路構成

## 2.3 FLASHROM

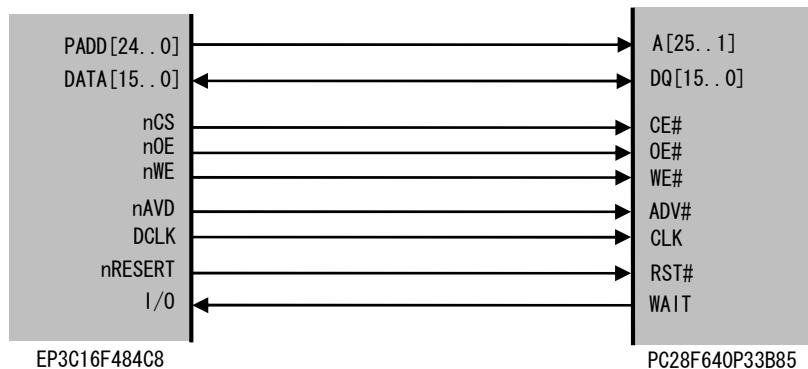

MS104-FPGA/C IIIには標準で8MByteのFLASHROM PC28F640P33(numonyx(Intel)製)が搭載されています。EP3C16F484とは16ビットバスで接続されており、コンフィギュレーションメモリ、プログラムメモリをして使用できます。

FLASHROMの書き込み方法についてはアプリケーションノート「AN1201 FLASHROMの書き込み方法」を参照してください。

Fig 2.3-1 FLASHROM インタフェース回路構成

| 信号名    | BANK | 接続ピン | 備考 <sup>*1</sup> | 信号名          | BANK | 接続ピン | 備考 <sup>*1</sup> |

|--------|------|------|------------------|--------------|------|------|------------------|

| PADD24 | 8    | C10  |                  | PADDO        | 7    | B18  |                  |

| PADD23 | 6    | G18  |                  | DATA15       | 8    | B6   |                  |

| PADD22 | 6    | B22  |                  | DATA14       | 8    | C8   |                  |

| PADD21 | 6    | B21  |                  | DATA13       | 8    | C7   |                  |

| PADD20 | 6    | C20  |                  | DATA12       | 8    | C4   |                  |

| PADD19 | 8    | A6   |                  | DATA11       | 8    | B3   |                  |

| PADD18 | 8    | A7   |                  | DATA10       | 8    | A3   |                  |

| PADD17 | 8    | B9   |                  | DATA9        | 8    | F8   |                  |

| PADD16 | 8    | A9   |                  | DATA8        | 8    | B4   |                  |

| PADD15 | 8    | B10  |                  | DATA7        | 8    | C6   |                  |

| PADD14 | 7    | F11  |                  | DATA6        | 8    | F10  |                  |

| PADD13 | 7    | E11  |                  | DATA5        | 8    | A5   |                  |

| PADD12 | 7    | B13  |                  | DATA4        | 8    | B7   |                  |

| PADD11 | 7    | A13  |                  | DATA3        | 8    | B8   |                  |

| PADD10 | 7    | B14  |                  | DATA2        | 8    | A8   |                  |

| PADD9  | 7    | A14  |                  | DATA1        | 1    | D1   |                  |

| PADD8  | 7    | D13  |                  | DATA0        | 1    | K1   |                  |

| PADD7  | 7    | C13  |                  | FLASH_nCE    | 1    | E2   | PU               |

| PADD6  | 7    | B15  |                  | FLASH_nOE    | 6    | E21  |                  |

| PADD5  | 7    | A15  |                  | FLASH_nWE    | 6    | E22  |                  |

| PADD4  | 7    | F13  |                  | FLASH_nAVD   | 6    | F20  | PD               |

| PADD3  | 7    | E14  |                  | FLASH_DCLK   | 1    | K2   | PU               |

| PADD2  | 7    | B17  |                  | FLASH_nRESET | 1    | F4   | PU               |

| PADD1  | 7    | A17  |                  | FLASH_WAIT   | 1    | F1   | PU               |

\*1 PU : Pull-Up      PD : Pull-Down

Table 2.3-1 FLASHROM 接続ピン

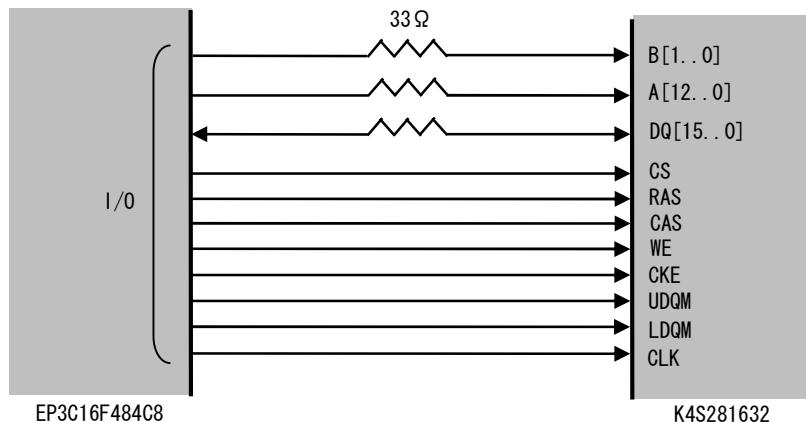

## 2.4 SDRAM

MS104-FPGA/C IIIには標準で 16MByte の SDRAM K4S281632(Samsung 製)が搭載されています。EP3C16F484 とは 16 ビットバスで接続されています。

MS104-FPGA/C IIIにはSDRAMを動作させるサンプル HDL ソースは付属しません。SDRAMを動作させるためには、EP3C16F484にSDRAMの IP を実装していただく必要があります。

Fig 2.4-1 SDRAM インタフェース回路構成

| 信号名    | BANK | 接続ピン | 備考 <sup>*1</sup> | 信号名     | BANK | 接続ピン | 備考 <sup>*1</sup> |

|--------|------|------|------------------|---------|------|------|------------------|

| SD_BA1 | 7    | F15  |                  | SD_D10  | 6    | H20  |                  |

| SD_BA0 | 7    | D15  |                  | SD_D9   | 6    | H19  |                  |

| SD_A12 | 7    | H13  |                  | SD_D8   | 6    | H18  |                  |

| SD_A11 | 7    | F12  |                  | SD_D7   | 6    | G17  |                  |

| SD_A10 | 7    | D17  |                  | SD_D6   | 6    | H17  |                  |

| SD_A9  | 7    | F14  |                  | SD_D5   | 6    | F17  |                  |

| SD_A8  | 7    | G16  |                  | SD_D4   | 6    | D20  |                  |

| SD_A7  | 7    | H12  |                  | SD_D3   | 6    | D21  |                  |

| SD_A6  | 7    | C15  |                  | SD_D2   | 6    | D22  |                  |

| SD_A5  | 7    | E15  |                  | SD_D1   | 6    | F21  |                  |

| SD_A4  | 7    | E16  |                  | SD_D0   | 6    | F22  |                  |

| SD_A3  | 7    | C17  |                  | SD_CS   | 7    | A16  |                  |

| SD_A2  | 7    | C9   |                  | SD_RAS  | 7    | B16  |                  |

| SD_A1  | 7    | B19  |                  | SD_CAS  | 7    | G12  |                  |

| SD_A0  | 7    | A19  |                  | SD_WE   | 7    | G13  |                  |

| SD_D15 | 6    | C22  |                  | SD_CKE  | 7    | G15  | PD               |

| SD_D14 | 6    | C21  |                  | SD_CLK  | 8    | E5   |                  |

| SD_D13 | 6    | J17  |                  | SD_UDQM | 7    | D19  |                  |

| SD_D12 | 6    | H16  |                  | SD_LDQM | 7    | G14  |                  |

| SD_D11 | 6    | J18  |                  |         |      |      |                  |

\*1 PD : Pull-Down

Table 2.4-1 SDRAM 接続ピン

## 2.5 LED

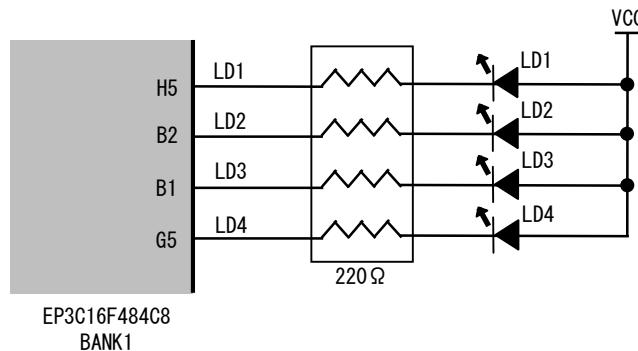

### 2.5.1 汎用モニタ LED

MS104-FPGA/C IIIには汎用モニタ LED4 個搭載されています。

Fig 2.5-1 汎用モニタ LED 回路構成

| 信号名 | BANK | 接続ピン |

|-----|------|------|

| LD1 | 1    | H5   |

| LD2 | 1    | B2   |

| LD3 | 1    | B1   |

| LD4 | 1    | G5   |

Table 2.5-1 汎用モニタ LED 接続ピン

| ポートの出力 | LED の状態 |

|--------|---------|

| LOW    | 点灯      |

| HIGH   | 消灯      |

Table 2.5-2 汎用モニタ LED の制御

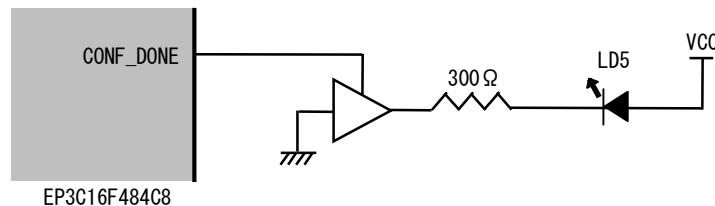

## 2.5.2 コンフィギュレーション状態 LED

MS104-FPGA/C IIIにはコンフィギュレーションの状態モニタ LED が 1 個搭載されています。

Fig 2.5-2 コンフィギュレーション状態 LED 回路構成

| LED の状態 | コンフィギュレーションの状態 |

|---------|----------------|

| 点灯      | コンフィギュレーション完了  |

| 消灯      | コンフィギュレーション中   |

Table 2.5-3 コンフィギュレーション状態 LED

| 信号名       | BANK | 接続ピン |

|-----------|------|------|

| CONF_DONE | 6    | M18  |

Table 2.5-4 コンフィギュレーション状態 LED 接続ピン

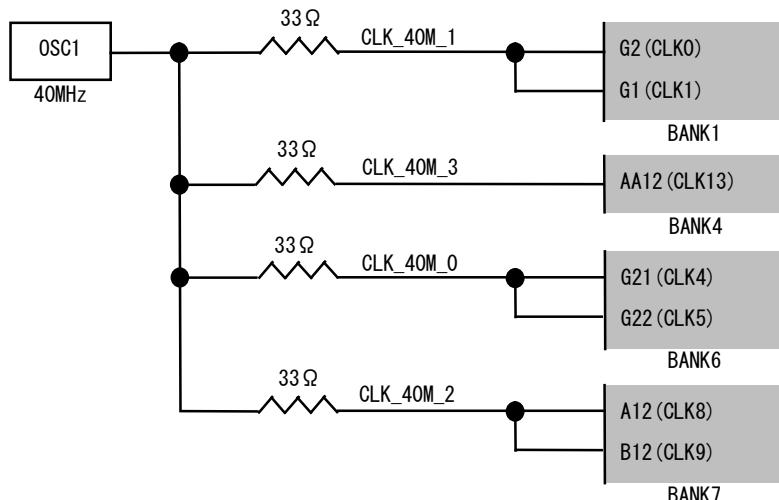

## 2.6 クロック

MS104-FPGA/C IIIには 40MHz の水晶発振器が実装されており、EP3C16F484 の各クロック入力ピンに接続されています。

Fig 2.6-1 クロック回路構成

| 信号名       | BANK | 接続ピン    |

|-----------|------|---------|

| CLK_40M_0 | 6    | G21、G22 |

| CLK_40M_1 | 1    | G1、G2   |

| CLK_40M_2 | 7    | A12、B12 |

| CLK_40M_3 | 4    | AA12    |

Table 2.6-1 クロック 接続ピン

## 2.7 操作スイッチ

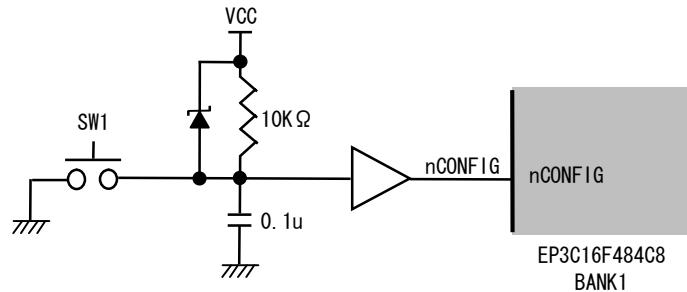

### 2.7.1 リコンフィギュレーションスイッチ

MS104-FPGA/C IIIにはリコンフィギュレーション用のプッシュスイッチが実装されています。リコンフィギュレーションスイッチ SW1 を押下すると、FPGA はリコンフィギュレーションを開始します。

Fig 2.7-1 リコンフィギュレーションスイッチ回路構成

| 信号名     | BANK | 接続ピン |

|---------|------|------|

| nCONFIG | 1    | K6   |

Table 2.7-1 リコンフィギュレーションスイッチ 接続ピン

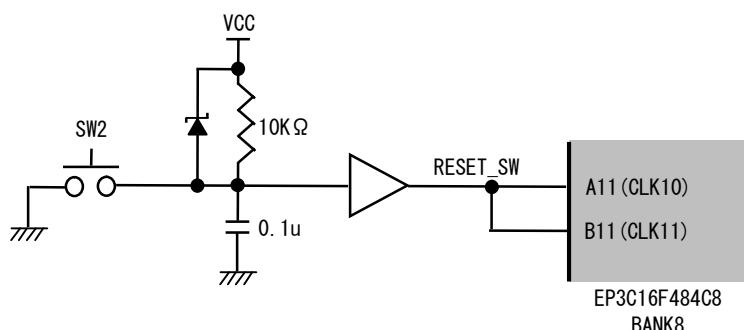

### 2.7.2 リセットスイッチ

MS104-FPGA/C IIIにはFPGA リセット用のプッシュスイッチが実装されています。SW2 を押下すると RESET\_SW 信号は LOW になります。

Fig 2.7-2 リセットスイッチ回路構成

| 信号名      | BANK | 接続ピン    |

|----------|------|---------|

| RESET_SW | 1    | A11、B11 |

Table 2.7-2 リセットスイッチ 接続ピン

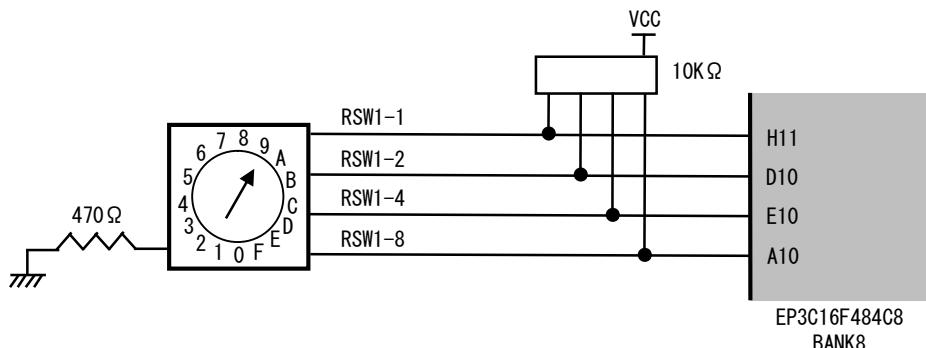

### 2.7.3 ロータリスイッチ

MS104-FPGA/C IIIには汎用ロータリスイッチが実装されています。

Fig 2.7-3 ロータリスイッチ回路構成

| 信号名    | BANK | 接続ピン |

|--------|------|------|

| RSW1-1 | 8    | H11  |

| RSW1-2 | 8    | D10  |

| RSW1-4 | 8    | E10  |

| RSW1-8 | 8    | A10  |

Table 2.7-3 ロータリスイッチ 接続ピン

| ポジション | RSW1-1 | RSW1-2 | RSW1-4 | RSW1-8 |

|-------|--------|--------|--------|--------|

| 0     | HIGH   | HIGH   | HIGH   | HIGH   |

| 1     | LOW    | HIGH   | HIGH   | HIGH   |

| 2     | HIGH   | LOW    | HIGH   | HIGH   |

| 3     | LOW    | LOW    | HIGH   | HIGH   |

| 4     | HIGH   | HIGH   | LOW    | HIGH   |

| 5     | LOW    | HIGH   | LOW    | HIGH   |

| 6     | HIGH   | LOW    | LOW    | HIGH   |

| 7     | LOW    | LOW    | LOW    | HIGH   |

| 8     | HIGH   | HIGH   | HIGH   | LOW    |

| 9     | LOW    | HIGH   | HIGH   | LOW    |

| A     | HIGH   | LOW    | HIGH   | LOW    |

| B     | LOW    | LOW    | HIGH   | LOW    |

| C     | HIGH   | HIGH   | LOW    | LOW    |

| D     | HIGH   | LOW    | LOW    | LOW    |

| E     | HIGH   | LOW    | LOW    | LOW    |

| F     | LOW    | LOW    | LOW    | LOW    |

Table 2.7-4 ロータリスイッチ信号状態

### 3. 外部インターフェース

#### 3.1 PC/104 バス

MS104-FPGA/C IIIはPC/104規格に準拠したPC/104バスインターフェースコネクタを搭載しています。FPGAにPC/104バスアクセス機能を実装することで、PC/104バスインターフェースを実現することができます。

また、PC/104バスを使用しない場合は汎用の拡張I/Oコネクタとして使用することができます。

| 機能        | 仕様                                               |

|-----------|--------------------------------------------------|

| コネクタ      | J1 PC104-64HK(未実装)<br>J2 PC104-40HK(未実装)         |

| PC/104モード | マスター/スレーブ両対応                                     |

| バススイッチ    | SN74CB3T3245PW(TI)<br>双方向バススイッチ<br>5.5Vトレラント入力対応 |

| 接続        | I/O 80本                                          |

Table 3.1-1 PC/104バス仕様概要

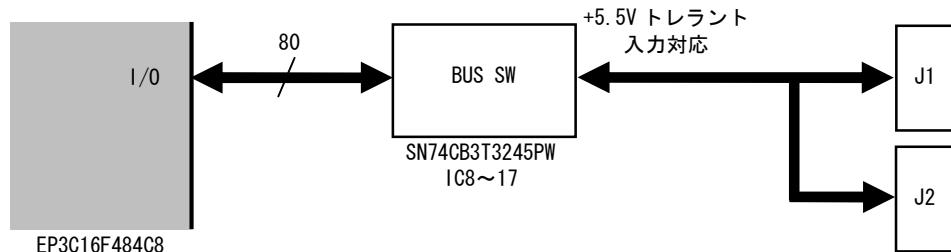

##### 3.1.1 PC/104バスインターフェース

PC/104バスインターフェース信号は、双方向バススイッチICを介してJ1、J2に信号が引き出されています。

Fig 3.1-1 PC/104バスインターフェース回路構成

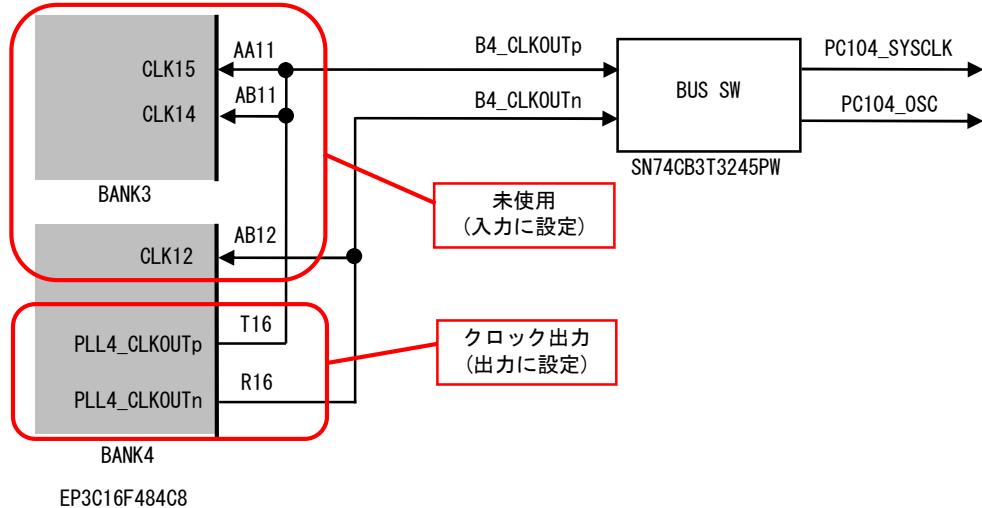

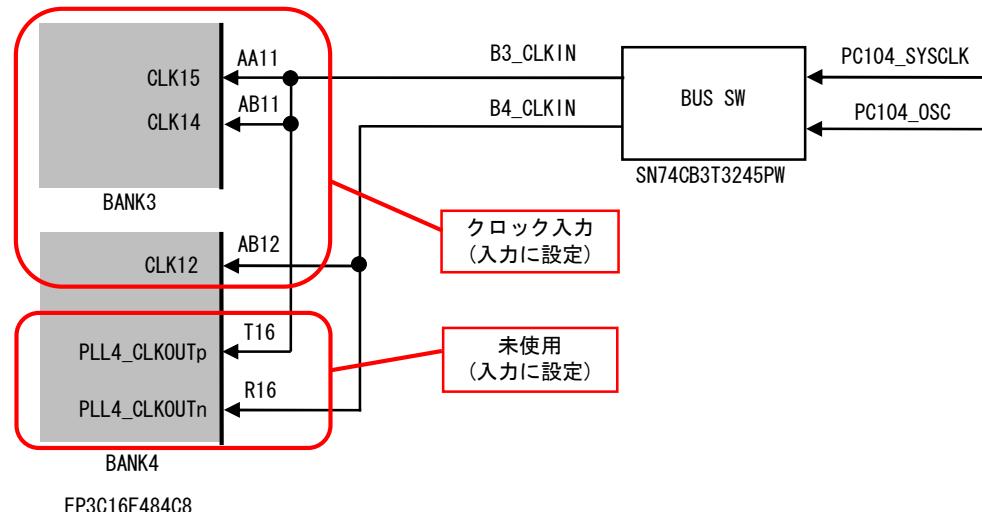

### 3.1.2 PC/104 バスクロック

PC/104 バスのクロックは以下のように構成されています。MS104-FPGA/C IIIをマスタとして使用する場合とスレーブとして使用する場合でFPGAのピンの入出力定義が変わりますのでご注意ください。スレーブとして使用する場合は、CLKOUT ピン (BANK4 T16, R16) は必ず入力ピンに設定してください。スレーブとして使用する場合、CLKOUT ピンを出力に設定すると CLKOUT 信号が PC104\_SYSCLK、PC104\_OSC 信号と衝突し、正常に動作せず、故障の原因となる場合があります。

Fig 3.1-2 PC/104 バスクロックの入出力(マスタとして使用時)

Fig 3.1-3 PC/104 バスクロックの入出力(スレーブとして使用時)

| No. | PC/104 信号名 | BANK | MS104-FPGA/C III<br>信号名 | 接続ピン          | 入出力*1  |        | 備考*2     |

|-----|------------|------|-------------------------|---------------|--------|--------|----------|

|     |            |      |                         |               | MASTER | SLAVE  |          |

| A1  | IOCHCHK    | 3    | B3_B1p                  | R9            | IN     | OUT    | PU/NC    |

| A2  | SD7        | 3    | B3_B1n                  | T8            | IN/OUT | IN/OUT |          |

| A3  | SD6        | 3    | B3_B2n                  | T9            | IN/OUT | IN/OUT |          |

| A4  | SD5        | 3    | B3_B14p                 | T10           | IN/OUT | IN/OUT |          |

| A5  | SD4        | 3    | B3_B7n                  | V7            | IN/OUT | IN/OUT |          |

| A6  | SD3        | 3    | B3_B7p                  | W6            | IN/OUT | IN/OUT |          |

| A7  | SD2        | 3    | B3_B3p                  | V6            | IN/OUT | IN/OUT |          |

| A8  | SD1        | 3    | B3_B3n                  | V5            | IN/OUT | IN/OUT |          |

| A9  | SD0        | 3    | B3_B2p                  | R10           | IN/OUT | IN/OUT |          |

| A10 | IOCHRDY    | 3    | B3_I06                  | T11           | IN     | OUT    | PU/NC    |

| A11 | AEN        | 3    | B3_B5p                  | R11           | OUT    | IN     |          |

| A12 | SA19       | 3    | B3_B4n                  | U8            | OUT    | IN     |          |

| A13 | SA18       | 3    | B3_B4p                  | U7            | OUT    | IN     |          |

| A14 | SA17       | 3    | B3_I03                  | W8            | OUT    | IN     |          |

| A15 | SA16       | 3    | B3_B11n                 | V8            | OUT    | IN     |          |

| A16 | SA15       | 3    | B3_B10p                 | W7            | OUT    | IN     |          |

| A17 | SA14       | 3    | B3_I04                  | V9            | OUT    | IN     |          |

| A18 | SA13       | 3    | B3_I05                  | V10           | OUT    | IN     |          |

| A19 | SA12       | 3    | B3_B17n                 | W10           | OUT    | IN     |          |

| A20 | SA11       | 3    | B3_B17p                 | V11           | OUT    | IN     |          |

| A21 | SA10       | 3    | B3_B11p                 | U9            | OUT    | IN     |          |

| A22 | SA9        | 3    | B3_B14n                 | U10           | OUT    | IN     |          |

| A23 | SA8        | 3    | B3_I07                  | U11           | OUT    | IN     |          |

| A24 | SA7        | 3    | B3_B5n                  | R12           | OUT    | IN     |          |

| A25 | SA6        | 4    | B3_B28p                 | T14           | OUT    | IN     |          |

| A26 | SA5        | 4    | B3_B29p                 | W17           | OUT    | IN     |          |

| A27 | SA4        | 4    | B3_B28n                 | T15           | OUT    | IN     |          |

| A28 | SA3        | 4    | B3_B23p                 | U12           | OUT    | IN     |          |

| A29 | SA2        | 4    | B3_B26p                 | U13           | OUT    | IN     |          |

| A30 | SA1        | 4    | B3_B31n                 | U14           | OUT    | IN     |          |

| A31 | SA0        | 4    | B3_B31p                 | U15           | OUT    | IN     |          |

| A32 | OV         |      | GND                     |               |        |        |          |

| B1  | OV         |      | GND                     |               |        |        |          |

| B2  | RESETDRV   | 3    | B3_B6p                  | Y3            | OUT    | IN     |          |

| B3  | +5V        |      | +5V                     |               |        |        |          |

| B4  | IRQ9       | 3    | B3_I01                  | Y4            | IN     | OUT    | PU/PD/NC |

| B5  | -5V        |      | NC                      |               |        |        |          |

| B6  | DRQ2       | 3    | B3_B8n                  | AB4           | IN     | OUT    |          |

| B7  | -12V       |      | NC                      |               |        |        |          |

| B8  | ENDXFR     |      | NC                      |               | IN     | OUT    | PU/NC    |

| B9  | +12V       |      | NC                      |               |        |        |          |

| B10 | (KEY)      |      | NC                      |               |        |        |          |

| B11 | SMEMW      | 3    | B3_B8p                  | AA4           | OUT    | IN     |          |

| B12 | SMEMR      | 3    | B3_B9p                  | AA5           | OUT    | IN     |          |

| B13 | IOW        | 3    | B3_B9n                  | AB5           | OUT    | IN     |          |

| B14 | IOR        | 3    | B3_I02                  | Y6            | OUT    | IN     |          |

| B15 | DACK3      | 3    | B3_B10n                 | Y7            | OUT    | IN     | PU/NC    |

| B16 | DRQ3       | 4    | B4_B23n                 | T12           | IN     | OUT    |          |

| B17 | DACK1      | 4    | B4_I02                  | R13           | OUT    | IN     | PU/NC    |

| B18 | DRQ1       | 4    | B4_B32p                 | R14           | IN     | OUT    |          |

| B19 | REFRESH    |      | NC                      |               | OUT    | IN     | PU/NC    |

| B20 | SYSCLK     | 3, 4 | B3_CLKIN/B4_CLKOUTp*3   | AA11 AB11 T16 | OUT    | IN     |          |

| B21 | IRQ7       | 4    | B4_B32n                 | R15           | IN     | OUT    | PU/PD/NC |

| B22 | IRQ6       | 4    | B4_I01                  | V12           | IN     | OUT    | PU/PD/NC |

| B23 | IRQ5       | 4    | B4_B21p                 | W13           | IN     | OUT    | PU/PD/NC |

| B24 | IRQ4       | 4    | B4_I03                  | V13           | IN     | OUT    | PU/PD/NC |

| B25 | IRQ3       | 4    | B4_I04                  | W14           | IN     | OUT    | PU/PD/NC |

| B26 | DACK2      | 4    | B4_B26n                 | V14           | OUT    | IN     | PU/NC    |

| B27 | TC         | 4    | B4_B27n                 | W15           | OUT    | IN     | PU/NC    |

| B28 | BALE       | 4    | B4_B27p                 | V15           | OUT    | IN     |          |

| B29 | +5V        |      | +5V                     |               |        |        |          |

| B30 | OSC        | 4    | B4_CLKIN/B4_CLKOUTn*3   | AB12 R16      | OUT    | IN     | PU/NC    |

| B31 | OV         |      | GND                     |               |        |        |          |

| B32 | OV         |      | GND                     |               |        |        |          |

\*1 PC/104 バスとして使用しない場合、I/O は入出力を任意に設定してお使いいただけます。

\*2 PU : Pull-Up PD : Pull-Down

\*3 PC/104 バスのクロックにつきましては「3.1.2 PC/104 バスクロック」を参照してください。

Table 3.1-2 PC/104 バスインタフェースコネクタ J1 ピンアサイン

| No. | PC/104 信号名 | BANK | 接続 I/O 信号名 | 接続ピン | 入出力*1  |        | 備考*2     |

|-----|------------|------|------------|------|--------|--------|----------|

|     |            |      |            |      | MASTER | SLAVE  |          |

| C0  | OV         |      | GND        |      |        |        |          |

| C1  | SBHE       | 3    | B3_B12n    | AB7  | OUT    | IN     |          |

| C2  | LA23       | 3    | B3_B12p    | AA7  | OUT    | IN     |          |

| C3  | LA22       | 3    | B3_B13p    | Y8   | OUT    | IN     |          |

| C4  | LA21       | 3    | B3_B15n    | AB8  | OUT    | IN     |          |

| C5  | LA20       | 3    | B3_B15p    | AA8  | OUT    | IN     |          |

| C6  | LA19       | 3    | B3_B16p    | AA9  | OUT    | IN     |          |

| C7  | LA18       | 3    | B3_B16n    | AB9  | OUT    | IN     |          |

| C8  | LA17       | 3    | B3_B18p    | Y10  | OUT    | IN     |          |

| C9  | MEMR       | 4    | B4_B20n    | AB14 | OUT    | IN     |          |

| C10 | MEMW       | 4    | B4_B20p    | AA14 | OUT    | IN     |          |

| C11 | SD8        | 4    | B4_B22n    | AB15 | IN/OUT | IN/OUT |          |

| C12 | SD9        | 4    | B4_B20p    | AA15 | IN/OUT | IN/OUT |          |

| C13 | SD10       | 4    | B4_B24n    | AB16 | IN/OUT | IN/OUT |          |

| C14 | SD11       | 4    | B4_B24p    | AA16 | IN/OUT | IN/OUT |          |

| C15 | SD12       | 4    | B4_B25n    | AB17 | IN/OUT | IN/OUT |          |

| C16 | SD13       | 4    | B4_B25p    | AA17 | IN/OUT | IN/OUT |          |

| C17 | SD14       | 4    | B4_B29n    | Y17  | IN/OUT | IN/OUT |          |

| C18 | SD15       | 4    | B4_I05     | AB18 | IN/OUT | IN/OUT |          |

| C19 | (KEY2)     |      | NC         |      |        |        |          |

| D0  | OV         |      | GND        |      |        |        |          |

| D1  | MEMCS16    | 4    | B4_B30p    | AA20 | IN     | OUT    | PU/NC    |

| D2  | IOCS16     | 4    | B4_B30n    | AB20 | IN     | OUT    | PU/NC    |

| D3  | IRQ10      | 4    | B4_I07     | AA19 | IN     | OUT    | PU/PD/NC |

| D4  | IRQ11      | 4    | B4_I08     | AB19 | IN     | OUT    | PU/PD/NC |

| D5  | IRQ12      | 3    | B3_B18n    | AA10 | IN     | OUT    | PU/PD/NC |

| D6  | IRQ15      | 3    | B3_I08     | AB10 | IN     | OUT    | PU/PD/NC |

| D7  | IRQ14      | 4    | B4_B19n    | AB13 | IN     | OUT    | PU/PD/NC |

| D8  | DACK0      | 4    | B4_B19p    | AA13 | OUT    | IN     |          |

| D9  | DRQ0       | 4    | B4_B21n    | Y13  | IN     | OUT    | PD       |

| D10 | DACK5      |      | NC         |      | OUT    | IN     | PU/NC    |

| D11 | DRQ5       |      | NC         |      |        |        |          |

| D12 | DACK6      |      | NC         |      |        |        | PU/NC    |

| D13 | DRQ6       |      | NC         |      |        |        |          |

| D14 | DACK7      |      | NC         |      |        |        | PU/NC    |

| D15 | DRQ7       |      | NC         |      |        |        |          |

| D16 | +5V        |      | +5V        |      |        |        |          |

| D17 | MASTER     | 4    | B4_I06     | AA18 | IN     | OUT    | PU/NC    |

| D18 | OV         |      | GND        |      |        |        |          |

| D19 | OV         |      | GND        |      |        |        |          |

\*1 PC/104 バスとして使用しない場合、I/O は入出力を任意に設定してお使いいただけます。

\*2 PU : Pull-Up PD : Pull-Down

Table 3.1-3 PC/104 バスインターフェースコネクタ J2 ピンアサイン

### 3.1.2 汎用 I/O として使用する場合

PC/104 バスインターフェースを使用しない場合、J1、J2 の各信号は汎用 I/O として使用することができます。ただし、その場合は MS104-SH4AG 等の PC/104 規格準拠ボードとは接続することはできませんのでご注意ください。

## 3.2 拡張 I/O

MS104-FPGA/C IIIはFPGAのI/O信号を拡張コネクタに引き出してあります。DIFFIO端子は、n端子、p端子を対にして、差動インピーダンス100Ωで設計されていますので、LVDS等にもご利用いただけます。

| 機能    | 仕様                                                                     |

|-------|------------------------------------------------------------------------|

| コネクタ  | J3、J4 FX2C-80S-1.27DSA/ヒロセまたは1.27 x 1.905mm ピッチ千鳥コネクタ<br>またはPC104-40HK |

| I/O   | I/O 112本                                                               |

| 差動I/O | 差動インピーダンス100Ω                                                          |

| I/O電圧 | BANK1、6 3.3V<br>BANK2、5 1.2/1.5/1.8/2.5/3.0/3.3V(DSW1、JP1、JP2にて設定)     |

Table 3.2-1 拡張I/O仕様概要

### 3.2.1 拡張I/Oインターフェース

MS104-FPGAのI/O拡張コネクタJ3、J4にはBANK1、2、5、6のI/O信号が引き出されています。BANK2、5のI/O電圧はスイッチの設定で切り替えることができます。I/O電圧の設定は「2.2.2 I/O BANK電圧の設定」を参照してください。

Fig 3.2-1 拡張I/Oインターフェース回路構成

| No. | 信号名          | BANK | 接続ピン | DIFFIO*1 | 備考*2 | No. | 信号名          | BANK | 接続ピン | DIFFIO*1 | 備考*2 |

|-----|--------------|------|------|----------|------|-----|--------------|------|------|----------|------|

| A1  | GND          |      |      |          |      | B1  | GND          |      |      |          |      |

| A2  | PLL1_CLKOUTp | 3    | AA3  |          |      | B2  | PLL1_CLKOUTn | 3    | AB3  |          |      |

| A3  | B1_L3p       | 1    | C2   | L3p      |      | B3  | B1_L3n       | 1    | C1   | L3n      |      |

| A4  | B1_L5p       | 1    | H6   | L5p      |      | B4  | B1_L5n       | 1    | J6   | L5n      |      |

| A5  | B1_L7p       | 1    | F2   | L7p      |      | B5  | B1_L7n       | 1    | F1   | L7n      |      |

| A6  | B1_L8p       | 1    | G4   | L8p      |      | B6  | B1_L8n       | 1    | G3   | L8n      |      |

| A7  | GND          |      |      |          |      | B7  | GND          |      |      |          |      |

| A8  | B1_L9p       | 1    | L8   | L9p      |      | B8  | B1_L9n       | 1    | K8   | L9n      |      |

| A9  | B1_L10p      | 1    | J7   | L10p     |      | B9  | B1_L10n      | 1    | K7   | L10n     |      |

| A10 | B1_L11p      | 1    | H2   | L11p     |      | B10 | B1_L11n      | 1    | H1   | L11n     |      |

| A11 | B1_L12p      | 1    | J2   | L12p     |      | B11 | B1_L12n      | 1    | J1   | L12n     |      |

| A12 | VCC          |      |      |          |      | B12 | VCC          |      |      |          |      |

| A13 | GND          |      |      |          |      | B13 | GND          |      |      |          |      |

| A14 | B2_L13p      | 2    | L6   | L13p     |      | B14 | B2_L13n      | 2    | M6   | L13n     |      |

| A15 | B2_L14p      | 2    | M2   | L14p     |      | B15 | B2_L14n      | 2    | M1   | L14n     |      |

| A16 | B2_L23p      | 2    | M8   | L23p     |      | B16 | B2_L23n      | 2    | N7   | L23n     |      |

| A17 | B2_L16p      | 2    | N2   | L16p     |      | B17 | B2_L16n      | 2    | N1   | L16n     |      |

| A18 | GND          |      |      |          |      | B18 | GND          |      |      |          |      |

| A19 | B2_I01       | 2    | M5   |          |      | B19 | B2_I02       | 2    | T3   |          |      |

| A20 | B2_L15p      | 2    | M4   | L15p     |      | B20 | B2_L15n      | 2    | M3   | L15n     |      |

| A21 | B2_L17p      | 2    | P2   | L17p     |      | B21 | B2_L17n      | 2    | P1   | L17n     |      |

| A22 | B2_L26p      | 2    | N7   | L26p     |      | B22 | B2_L26n      | 2    | P7   | L26n     |      |

| A23 | GND          |      |      |          |      | B23 | GND          |      |      |          |      |

| A24 | B2_L22p      | 2    | N6   | L22p     |      | B24 | B2_L22n      | 2    | M7   | L22n     |      |

| A25 | B2_L20p      | 2    | U2   | L20p     |      | B25 | B2_L20n      | 2    | U1   | L20n     |      |

| A26 | B2_L19p      | 2    | P4   | L19p     |      | B26 | B2_L19n      | 2    | P3   | L19n     |      |

| A27 | B2_L28p      | 2    | P6   | L28p     |      | B27 | B2_L28n      | 2    | R5   | L28n     |      |

| A28 | GND          |      |      |          |      | B28 | GND          |      |      |          |      |

| A29 | B2_L25p      | 2    | Y2   | L25p     |      | B29 | B2_L25n      | 2    | Y1   | L25n     |      |

| A30 | B2_L18p      | 2    | R2   | L18p     |      | B30 | B2_L18n      | 2    | R1   | L18n     |      |

| A31 | B2_L27p      | 2    | AA2  | L27p     |      | B31 | B2_L27n      | 2    | AA1  | L27n     |      |

| A32 | B2_L30p      | 2    | R7   | L30p     |      | B32 | B2_L30n      | 2    | T7   | L30n     |      |

| A33 | GND          |      |      |          |      | B33 | GND          |      |      |          |      |

| A34 | B2_I03       | 2    | V4   |          |      | B34 | B2_I04       | 2    | V3   |          |      |

| A35 | B2_L29p      | 2    | T5   | L29p     |      | B35 | B2_L29n      | 2    | R6   | L29n     |      |

| A36 | B2_L21p      | 2    | V2   | L21p     |      | B36 | B2_L21n      | 2    | V1   | L21n     |      |

| A37 | B2_L24p      | 2    | W2   | L24p     |      | B37 | B2_L24n      | 2    | W1   | L24n     |      |

| A38 | VCCIO_B2     | 2    |      |          |      | B38 | VCCIO_B2     | 2    |      |          |      |

| A39 | GND          |      |      |          |      | B39 | GND          |      |      |          |      |

| A40 | B2_CLK2      | 2    | T2   | CLK_1p   | PU   | B40 | B2_CLK3      | 2    | T1   | CLK_1n   | PU   |

\*1 DIFFIO : 対となる p、n は基板上で差動インピーダンス 100Ω となっています。

\*2 PU : Pull-Up PD : Pull-Down

Table 3.2-2 拡張 I/O コネクタ J3 ピンアサイン

| No. | 信号名          | BANK | 接続ピン | DIFFIO*1 | 備考*2 | No. | 信号名          | BANK | 接続ピン | DIFFIO*1 | 備考*2 |

|-----|--------------|------|------|----------|------|-----|--------------|------|------|----------|------|

| A1  | B5_CLK6      | 5    | T21  | CLK_3p   | PU   | B1  | B5_CLK7      | 5    | T22  | CLK_3n   | PU   |

| A2  | GND          |      |      |          |      | B2  | GND          |      |      |          |      |

| A3  | VCC10_B5     | 5    |      |          |      | B3  | VCC10_B5     | 5    |      |          |      |

| A4  | B5_R35n      | 5    | AA22 | R35n     |      | B4  | B5_R35p      | 5    | AA21 | R35p     |      |

| A5  | B5_I01       | 5    | T17  |          |      | B5  | B5_I02       | 5    | T18  |          |      |

| A6  | B5_R34n      | 5    | W20  | R34n     |      | B6  | B5_R34p      | 5    | W19  | R34p     |      |

| A7  | B5_R33n      | 5    | Y22  | R33n     |      | B7  | B5_R33p      | 5    | Y21  | R33p     |      |

| A8  | GND          |      |      |          |      | B8  | GND          |      |      |          |      |

| A9  | B5_R31n      | 5    | W22  | R31n     |      | B9  | B5_R31p      | 5    | W21  | R31p     |      |

| A10 | B5_R32n      | 5    | U20  | R32n     |      | B10 | B5_R32p      | 5    | U19  | R32p     |      |

| A11 | B5_R27n      | 5    | U22  | R27n     |      | B11 | B5_R27p      | 5    | U21  | R27p     |      |

| A12 | B5_I03       | 5    | N14  |          |      | B12 | B5_I04       | 5    | R17  |          |      |

| A13 | GND          |      |      |          |      | B13 | GND          |      |      |          |      |

| A14 | B5_R26n      | 5    | R18  | R26n     |      | B14 | B5_R26p      | 5    | R19  | R26p     |      |

| A15 | B5_R28n      | 5    | V22  | R28n     |      | B15 | B5_R28p      | 5    | V21  | R28p     |      |

| A16 | B5_R30n      | 5    | P15  | R30n     |      | B16 | B5_R30p      | 5    | P16  | R30p     |      |

| A17 | B5_R23n      | 5    | N20  | R23n     |      | B17 | B5_R23p      | 5    | N19  | R23p     |      |

| A18 | GND          |      |      |          |      | B18 | GND          |      |      |          |      |

| A19 | B5_R25n      | 5    | R22  | R25n     |      | B19 | B5_R25p      | 5    | R21  | R25p     |      |

| A20 | B5_I05       | 5    | N16  |          |      | B20 | B5_I06       | 5    | P20  |          |      |

| A21 | B5_R24n      | 5    | P22  | R24n     |      | B21 | B5_R24p      | 5    | P21  | R24p     |      |

| A22 | B5_R22n      | 5    | N17  | R22n     |      | B22 | B5_R22p      | 5    | N18  | R22p     |      |

| A23 | GND          |      |      |          |      | B23 | GND          |      |      |          |      |

| A24 | B5_R29n      | 5    | M15  | R29n     |      | B24 | B5_R29p      | 5    | N15  | R29p     |      |

| A25 | B5_R21n      | 5    | N22  | R21n     |      | B25 | B5_R21p      | 5    | N21  | R21p     |      |

| A26 | B5_R20n      | 5    | M22  | R20n     |      | B26 | B5_R20p      | 5    | M21  | R20p     |      |

| A27 | B5_R19n      | 5    | M20  | R19n     |      | B27 | B5_R19p      | 5    | M19  | R19p     |      |

| A28 | GND          |      |      |          |      | B28 | GND          |      |      |          |      |

| A29 | VCC          |      |      |          |      | B29 | VCC          |      |      |          |      |

| A30 | B6_R18n      | 6    | L16  | R18n     |      | B30 | B6_R18p      | 6    | L15  | R18p     |      |

| A31 | B6_R17n      | 6    | L22  | R17n     |      | B31 | B6_R17p      | 6    | L21  | R17p     |      |

| A32 | B6_I01       | 6    | K15  |          |      | B32 | B6_I02       | 6    | K19  |          |      |

| A33 | B6_R16n      | 6    | K22  | R16n     |      | B33 | B6_R16p      | 6    | K21  | R16p     |      |

| A34 | GND          |      |      |          |      | B34 | GND          |      |      |          |      |

| A35 | B6_R15n      | 6    | J22  | R15n     |      | B35 | B6_R15p      | 6    | J21  | R15p     |      |

| A36 | B6_R14n      | 6    | J16  | R14n     |      | B36 | B6_R14p      | 6    | K16  | R14p     |      |

| A37 | B6_R13n      | 6    | H22  | R13n     |      | B37 | B6_R13p      | 6    | H21  | R13p     |      |

| A38 | B6_R12n      | 6    | K17  | R12n     |      | B38 | B6_R12p      | 6    | K18  | R12p     |      |

| A39 | PLL2_CLKOUTn | 7    | A20  |          |      | B39 | PLL2_CLKOUTp | 7    | B20  |          |      |

| A40 | GND          |      |      |          |      | B40 | GND          |      |      |          |      |

\*1 DIFFIO : 対となる p、n は基板上で差動インピーダンス 100Ω となっています。

\*2 PU : Pull-Up PD : Pull-Down

Table 3.2-3 拡張 I/O コネクタ J4 ピンアサイン

### 3.2.2 接続例

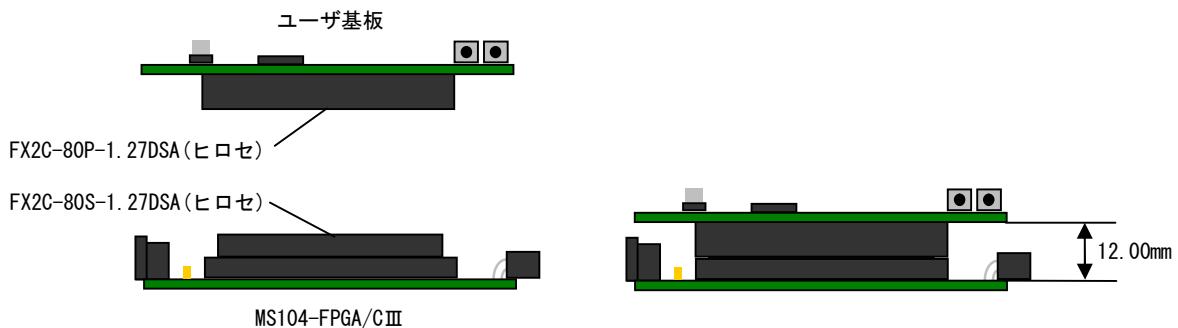

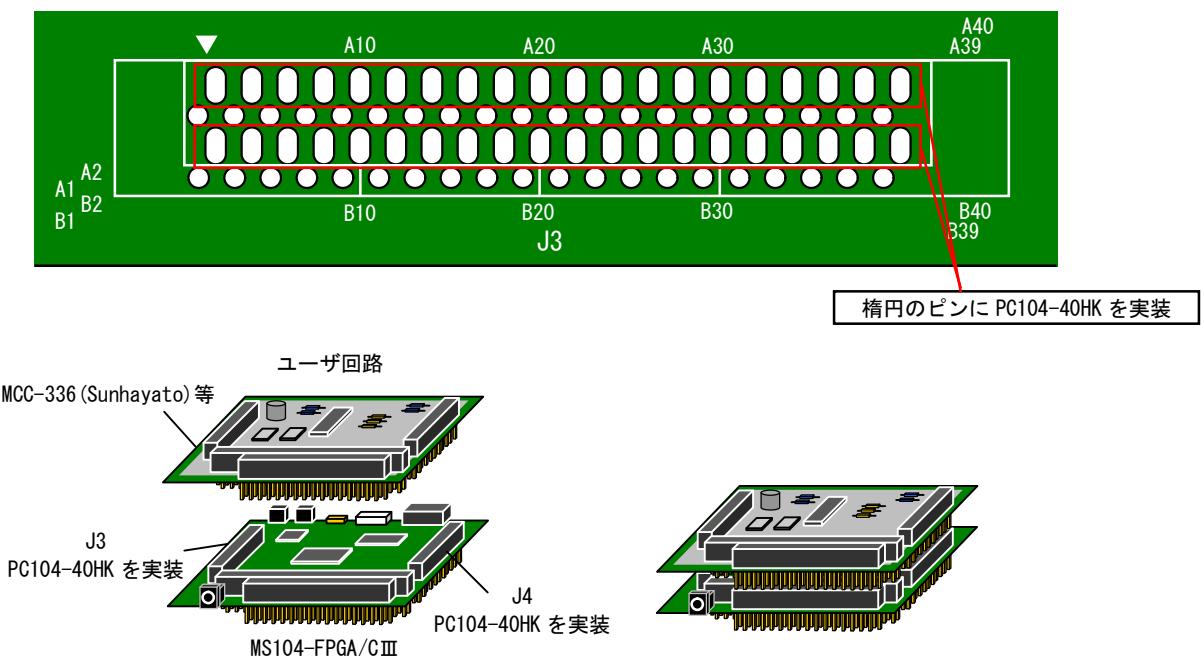

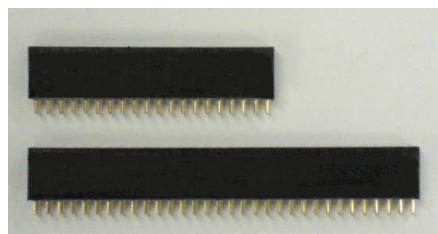

MS104-FPGA/C III の I/O 拡張コネクタ J3、J4 は出荷時には未実装になっています。FX2C シリーズ(ヒロセ)の他、各社の 1.27 x 1.905 mm ピッチ千鳥コネクタ、または PC104-40HK を実装することができます。以下に接続例を示します。

① FX2C シリーズまたは 1.27 x 1.905 mm ピッチコネクタを実装して接続する場合

Fig 3.2-2 拡張 I/O コネクタ接続例 1

② PC104-40HK を実装して接続する場合

MS104-FPGA/C III の I/O 拡張コネクタ J3、J4 は PC104-40HK を実装することができます。J3、J4 に PC104-40HK を実装することにより、Sunhayato 社製 PC/104 規格ユニバーサル基板「MCC-336」等と接続することができ、ユニバーサル基板に I/O を拡張し、自由に回路を作成することができます。ただし、J3、J4 に PC104-40HK を実装した場合、使用できる I/O 数は半分となります。

Fig 3.2-3 拡張 I/O コネクタ接続例 2

| No. | 信号名          | BANK | 接続ピン | DIFFIO*1 | 備考*2 | No. | 信号名          | BANK | 接続ピン | DIFFIO*1 | 備考*2 |

|-----|--------------|------|------|----------|------|-----|--------------|------|------|----------|------|

| A2  | PLL1_CLKOUTp | 3    | AA3  |          |      | B2  | PLL1_CLKOUTn | 3    | AB3  |          |      |

| A4  | B1_L5p       | 1    | H6   | L5p      |      | B4  | B1_L5n       | 1    | J6   | L5n      |      |

| A6  | B1_L8p       | 1    | G4   | L8p      |      | B6  | B1_L8n       | 1    | G3   | L8n      |      |

| A8  | B1_L9p       | 1    | L8   | L9p      |      | B8  | B1_L9n       | 1    | K8   | L9n      |      |

| A10 | B1_L11p      | 1    | H2   | L11p     |      | B10 | B1_L11n      | 1    | H1   | L11n     |      |

| A12 | VCC          |      |      |          |      | B12 | VCC          |      |      |          |      |

| A14 | B2_L13p      | 2    | L6   | L13p     |      | B14 | B2_L13n      | 2    | M6   | L13n     |      |

| A16 | B2_L23p      | 2    | M8   | L23p     |      | B16 | B2_L23n      | 2    | N7   | L23n     |      |

| A18 | GND          |      |      |          |      | B18 | GND          |      |      |          |      |

| A20 | B2_L15p      | 2    | M4   | L15p     |      | B20 | B2_L15n      | 2    | M3   | L15n     |      |

| A22 | B2_L26p      | 2    | N7   | L26p     |      | B22 | B2_L26n      | 2    | P7   | L26n     |      |

| A24 | B2_L22p      | 2    | N6   | L22p     |      | B24 | B2_L22n      | 2    | M7   | L22n     |      |

| A26 | B2_L19p      | 2    | P4   | L19p     |      | B26 | B2_L19n      | 2    | P3   | L19n     |      |

| A28 | GND          |      |      |          |      | B28 | GND          |      |      |          |      |

| A30 | B2_L18p      | 2    | R2   | L18p     |      | B30 | B2_L18n      | 2    | R1   | L18n     |      |

| A32 | B2_L30p      | 2    | R7   | L30p     |      | B32 | B2_L30n      | 2    | T7   | L30n     |      |

| A34 | B2_I03       | 2    | V4   |          |      | B34 | B2_I04       | 2    | V3   |          |      |

| A36 | B2_L21p      | 2    | V2   | L21p     |      | B36 | B2_L21n      | 2    | V1   | L21n     |      |

| A38 | VCC10_B2     | 2    |      |          |      | B38 | VCC10_B2     | 2    |      |          |      |

| A40 | B2_CLK2      | 2    | T2   | CLK_1p   | PU   | B40 | B2_CLK3      | 2    | T1   | CLK_1n   | PU   |

Table 3.2-4 PC104-40HK を実装した場合の J3 コネクタピンアサイン

| No. | 信号名     | BANK | 接続ピン | DIFFIO*1 | 備考*2 | No. | 信号名     | BANK | 接続ピン | DIFFIO*1 | 備考*2 |

|-----|---------|------|------|----------|------|-----|---------|------|------|----------|------|

| A2  | GND     |      |      |          |      | B2  | GND     |      |      |          |      |

| A4  | B5_R35n | 5    | AA22 | R35n     |      | B4  | B5_R35p | 5    | AA21 | R35p     |      |

| A6  | B5_R34n | 5    | W20  | R34n     |      | B6  | B5_R34p | 5    | W19  | R34p     |      |

| A8  | GND     |      |      |          |      | B8  | GND     |      |      |          |      |

| A10 | B5_R32n | 5    | U20  | R32n     |      | B10 | B5_R32p | 5    | U19  | R32p     |      |

| A12 | B5_I03  | 5    | N14  |          |      | B12 | B5_I04  | 5    | R17  |          |      |

| A14 | B5_R26n | 5    | R18  | R26n     |      | B14 | B5_R26p | 5    | R19  | R26p     |      |

| A16 | B5_R30n | 5    | P15  | R30n     |      | B16 | B5_R30p | 5    | P16  | R30p     |      |

| A18 | GND     |      |      |          |      | B18 | GND     |      |      |          |      |

| A20 | B5_I05  | 5    | N16  |          |      | B20 | B5_I06  | 5    | P20  |          |      |

| A22 | B5_R22n | 5    | N17  | R22n     |      | B22 | B5_R22p | 5    | N18  | R22p     |      |

| A24 | B5_R29n | 5    | M15  | R29n     |      | B24 | B5_R29p | 5    | N15  | R29p     |      |

| A26 | B5_R20n | 5    | M22  | R20n     |      | B26 | B5_R20p | 5    | M21  | R20p     |      |

| A28 | GND     |      |      |          |      | B28 | GND     |      |      |          |      |

| A30 | B6_R18n | 6    | L16  | R18n     |      | B30 | B6_R18p | 6    | L15  | R18p     |      |

| A32 | B6_I01  | 6    | K15  |          |      | B32 | B6_I02  | 6    | K19  |          |      |

| A34 | GND     |      |      |          |      | B34 | GND     |      |      |          |      |

| A36 | B6_R14n | 6    | J16  | R14n     |      | B36 | B6_R14p | 6    | K16  | R14p     |      |

| A38 | B6_R12n | 6    | K17  | R12n     |      | B38 | B6_R12p | 6    | K18  | R12p     |      |

| A40 | GND     |      |      |          |      | B40 | GND     |      |      |          |      |

Table 3.2-5 PC104-40HK を実装した場合の J4 コネクタピンアサイン

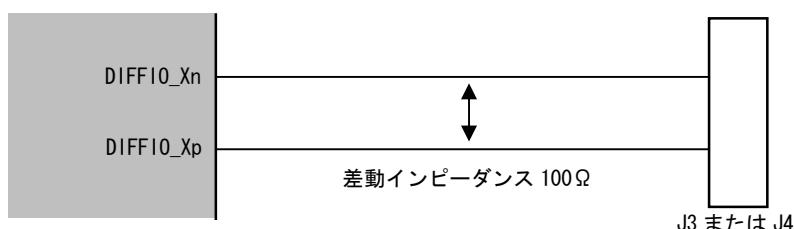

### 3.2.3 差動 I/O

EP3C16F484 は差動 I/O をサポートしています。MS104-FPGA/C III では差動 I/O を利用できるように基板上で対となる差動 I/O を差動インピーダンス 100Ω の差動配線をしています。

Fig 3.2-3 差動 I/O 回路構成

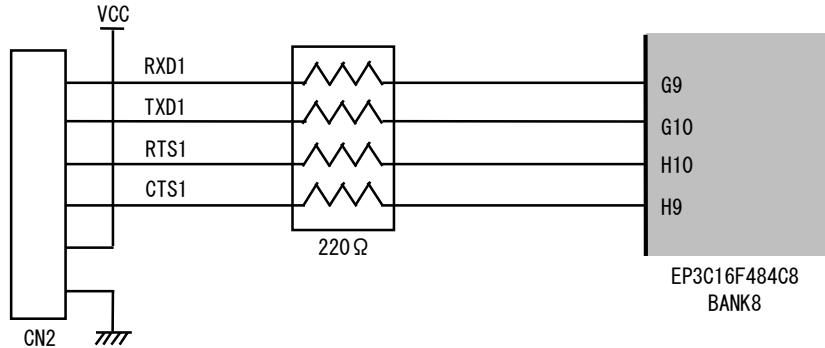

### 3.3 シリアルインタフェース

MS104-FPGA/C IIIにはシリアルインタフェース用コネクタが搭載されています。FPGAにシリアルインタフェース機能を実装することで弊社製インターフェースコンバータシリーズをお使いいただけます。シリアルインターフェースコンバータシリーズにつきましては「5 関連製品のご紹介」を参照してください。

Fig 3.3-1 シリアルインタフェース回路構成

| No. | 信号名  | BANK | 接続ピン |

|-----|------|------|------|

| 1   | RXD1 | 8    | G9   |

| 2   | TXD1 | 8    | G10  |

| 3   | RTS1 | 8    | H10  |

| 4   | CTS1 | 8    | H9   |

| 5   | VCC  |      |      |

| 6   | GND  |      |      |

Table 3.3-1 シリアルインタフェースコネクタ CN2 ピンアサイン

### 3.4 JTAG インタフェース

MS104-FPGA/C IIIには FPGA のコンフィギュレーション用の JTAG コネクタを搭載しています。ALTERA 社製「Byte-Blaster」、「USB-Blaster」等を接続し、JTAG 経由で FPGA のコンフィギュレーションをすることができます。

| No. | 信号名 | No. | 信号名   |

|-----|-----|-----|-------|

| 1   | TCK | 2   | GND   |

| 3   | TDO | 4   | +2.5V |

| 5   | TMS | 6   | NC    |

| 7   | NC  | 8   | NC    |

| 9   | TDI | 10  | GND   |

Table 3.4-1 JTAG インタフェースコネクタ CN1 ピンアサイン

### 3.5 電源

MS104-FPGA/C III 単一+5V で動作します。P1 または CN3 または PC/104 バスインターフェースコネクタ J1、J2 から+5V を供給します。

CN3 電源コネクタ

| No. | 信号名   |

|-----|-------|

| P   | +5V   |

| B   | (GND) |

| S   | GND   |

P1 DC ジャック

| No. | 信号名 |

|-----|-----|

| 1   | +5V |

| 2   | GND |

Table 3.5-1 電源コネクタピンアサイン

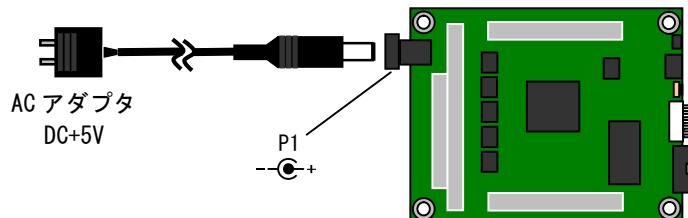

#### 3.5.1 P1 DC ジャックから電源を供給する場合

P1 DC ジャックから電源を供給する場合は、P1 に DC+5V の AC アダプタ等を接続し、電源を供給してください。

Fig 3.5-1 DC ジャック P1 からの電源供給例

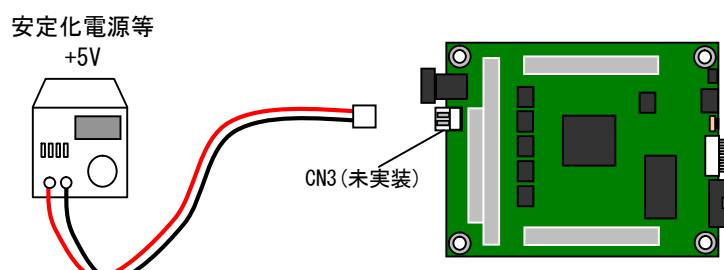

#### 3.5.2 CN3 電源コネクタから電源を供給する場合

CN3 電源コネクタ(未実装)から電源を供給する場合は、コネクタを実装し、DC+5V を供給してください。

Fig 3.5-2 電源コネクタ CN3 からの電源供給例

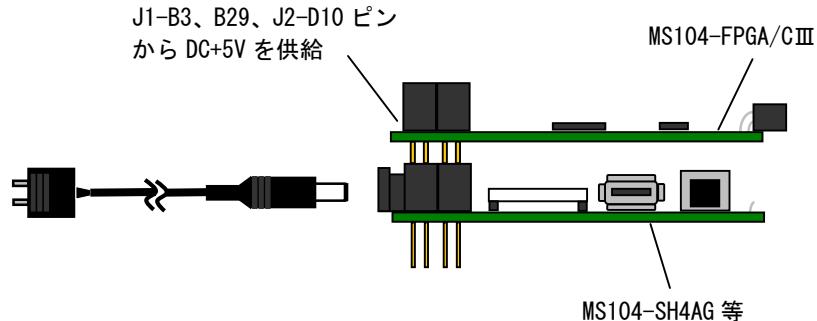

### 3.5.3 PC/104 バスインタフェースから電源を供給する場合

PC/104 バスインタフェースから電源を供給する場合は、J1、J2 に PC/104 コネクタを実装し、J1 の B3、B29 ピン、J2 の D16 ピンから電源を供給してください。この場合、MS104-FPGA/C III の電源コネクタから電源を供給しないでください。

Fig 3.5-3 PC/104 バスからの電源供給例

#### 4. テクニカルデータ

## 4.1 外形寸法

Fig 4.1-1 MS104-FPGA/CⅢ外形寸法図

## 4.2 PC/104 ボードの接続

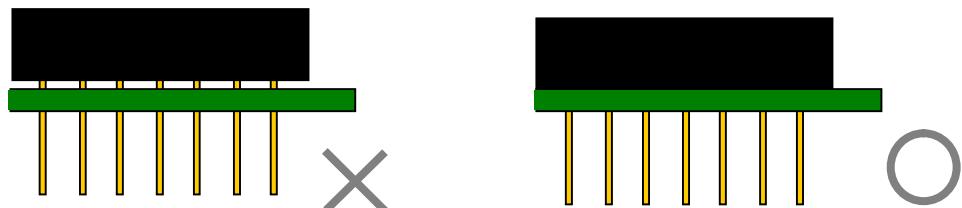

### 4.2.1 PC/104 コネクタの取り付け

PC/104 ボードを接続する場合には、別売りの PC/104 バスコネクタ(64pin 1 個、40pin 1 個)を実装してください。

実装する際には、基板にコネクタをしっかりと差し込んで、浮きがないように取り付けてください。

また、できるだけ細いハンダゴテを使用し、ピンの挿抜部分にハンダが付着しないように注意してください。

Fig 4.2-1 PC/104 コネクタの実装

### 4.2.2 PC/104 ボードの接続例

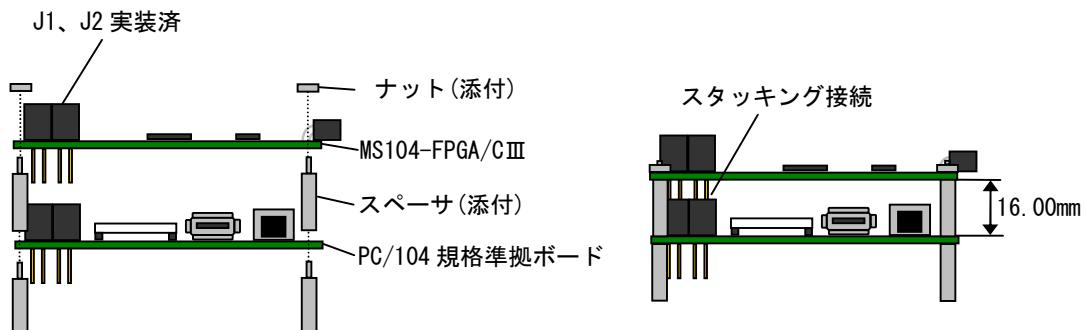

MS104-FPGA/C IIIは、弊社製 PC/104 規格準拠ボード、MS104-SH4AG、MS104-SH4、MS104-SH2 をはじめ、各社 PC/104 規格準拠ボードと接続して使用することができます。PC/104 ボードは、上下のどちらにでもスタッキングが可能です。

Fig 4.2-2 PC/104 規格準拠ボードとの接続例

## 5. 関連製品のご案内

### 5.1 関連製品

#### 5.1.1 MS104-SH4AG

MS104-SH4AG は、CPU に SH7764(ルネサステクノロジ製)を搭載した PC/104 規格準拠<sup>\*1</sup>ボードコンピュータです。多様なインターフェースを搭載し、標準 OS に Linux を採用しているので、高度な組み込みアプリケーションを容易に構築することができます。

| 機能             | 仕 様                                                                                    |

|----------------|----------------------------------------------------------------------------------------|

| CPU            | R5S77640N300BG (ルネサステクノロジ社製) SH-4A コア                                                  |

| クロック           | システムクロック 27.0000MHz 水晶発振器<br>CPU クロック 最大 324MHz<br>バスクロック 最大 108MHz<br>周辺クロック 最大 54MHz |

| メモリ            | FLASHROM 16MByte<br>SDRAM 64MByte                                                      |

| CPLD           | XC9572XL-7TQ100C(Xilinx 社製)                                                            |

| イーサネットインターフェース | 10/100BASE-T 1CH<br>EtherNET トランシーバ DP83848J(National Semiconductor 社製)                |

| USB インタフェース    | USB2.0 HOST (HIGH/FULL/LOW SPEED) 1CH                                                  |

| CF カードスロット     | CPU 内蔵 ATAPI インタフェース<br>TYPE I 1スロット                                                   |

| SD/MMC カードスロット | 1スロット SPI モード                                                                          |

| LCD コントローラ     | 最大解像度 1024x1024dot                                                                     |

| オーディオインターフェース  | CPU 内蔵シリアルサウンドインターフェース 4CH                                                             |

| シリアル I/F       | 調歩同期式 2CH                                                                              |

| I2C インタフェース    | CPU 内蔵 I2C インタフェース                                                                     |

| パラレルインターフェース   | I/O 8bit 3.3V CMOS                                                                     |

| RTC            | S-35190(SII 社製) 電気二重層コンデンサによりバックアップ                                                    |

| リセット           | リセット IC、リセット SW 搭載                                                                     |

| 外部拡張バス         | PC/104 準拠(一部非サポート)                                                                     |

| 電源電圧           | 5.0V±5%                                                                                |

| オプション電源        | DC -5V、+12V、-12V                                                                       |

| 寸法             | 90.2×95.9 mm                                                                           |

\*1 PC/104 規格と一部異なる部分があります。

### 5.1.2 MS104-SH4

MS104-SH4 は、CPU に SH7750R(ルネサステクノロジ製)を搭載した PC/104 規格準拠<sup>\*1</sup> ボードコンピュータです。標準 OS に Linux を採用しているので、高度な組み込みアプリケーションを容易に構築することができます。

| 機能             | 仕様                                                                           |

|----------------|------------------------------------------------------------------------------|

| CPU            | R5S7750RF240 (ルネサステクノロジ社製) SH-4 コア                                           |

| クロック           | システムクロック 19.6608MHz 水晶発振器<br>CPU クロック 最大 235.9296MHz<br>バスクロック 最大 58.9824MHz |

| メモリ            | FLASHROM 16MByte<br>SDRAM 64MByte                                            |

| CPLD           | EPM7128AETC100-10 (ALTERA 社製)                                                |

| イーサネットインターフェース | 10/100BASE-T 1CH<br>LAN91C111 (SMSC 社製)                                      |

| CF カードスロット     | CPU 内蔵 ATAPI インタフェース<br>TYPE I 1スロット                                         |

| シリアル I/F       | 調歩同期式 2CH                                                                    |

| I2C インタフェース    | CPU 内蔵 I2C インタフェース                                                           |

| パラレルインターフェース   | I/O 8bit 3.3V CMOS                                                           |

| RTC            | RS5C316 (RICOH 社製) 電気二重層コンデンサによりバックアップ                                       |

| リセット           | リセット IC、リセット SW 搭載                                                           |

| 外部拡張バス         | PC/104 準拠(一部非サポート)                                                           |

| 電源電圧           | 5.0V±5%                                                                      |

| オプション電源        | DC -5V、+12V、-12V                                                             |

| 寸法             | 90.2×95.9 mm                                                                 |

\*1 PC/104 規格と一部異なる部分があります。

### 5.1.3 MS104-SH2

MS104-SH4 は、CPU に SH7145F(ルネサステクノロジ製)を搭載した PC/104 標準準拠<sup>\*1</sup> ボードコンピュータです。標準 OS に μITRON4.0 準拠の TOPPERS/FI4 を採用しているので、リアルタイム性の高いシステムを容易に構築することができます。

| 機能             | 仕様                                                                       |

|----------------|--------------------------------------------------------------------------|

| CPU            | SH7145F50 (ルネサステクノロジ社製) SH-2 コア                                          |

| クロック           | システムクロック 12.288MHz 水晶発振器<br>CPU クロック 最大 49.152MHz<br>バスクロック 最大 49.152MHz |

| メモリ            | FLASHROM 外部 2MByte 内蔵 256KByte<br>SRAM 1MByte                            |

| CPLD           | EPM7128AETC100-10 (ALTERA 社製)                                            |

| イーサネットインターフェース | 10/100BASE-T 1CH<br>RTL8019AS (REALTEK 社製)                               |

| USB インタフェース    | USB1.1 FUNCTION 1CH                                                      |

| CF カードスロット     | CPU 内蔵 ATAPI インタフェース<br>TYPE I 1 スロット                                    |

| シリアル I/F       | 調歩同期式 3CH                                                                |

| I/O インタフェース    | I/O 16bit 3.3V<br>A/D ポート分解能 10bit 8 本                                   |

| RTC            | RS5C316A (RICOH 社製) 電気二重層コンデンサによりバックアップ                                  |

| リセット           | リセット IC、リセット SW 搭載                                                       |

| 外部拡張バス         | PC/104 準拠(一部非サポート)                                                       |

| 電源電圧           | 5.0V±5%                                                                  |

| オプション電源        | DC -5V、+12V、-12V                                                         |

| 寸法             | 90.2 × 95.9 mm                                                           |

\*1 PC/104 標格と一部異なる部分があります。

### 5.1.4 Linux 開発キット

MS104-SH4AG での Linux システム開発に必要なものがすべてセットになっていますので、すぐに開発に取り掛かることができます。Linux 開発環境に VMware Player を採用していますので、Windows 上で開発を行うことができます。

| キット内容         |                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------|

| DVD-ROM       | -Linux クロス開発環境<br>・ブートローダソースコード<br>・カーネルソースコード<br>・デバイスドライバソースコード<br>・GNU C クロスコンパイラ<br>・サンプルプログラム<br>・解説マニュアル一式 |

| Ethernet ケーブル |                                                                                                                  |

| RS232 ケーブル    |                                                                                                                  |

| CF メモリカード     |                                                                                                                  |

| AC アダプタ       |                                                                                                                  |

### 5.1.5 AC アダプタ

MS104-FPGA/C III や、MS104-SH4AG で使用できる AC アダプタです。

| 項目  | 仕様                    |

|-----|-----------------------|

| 入力  | AC100V                |

| 出力  | DC5V/2A               |

| その他 | RoHS 対応<br>PSE 認定取得済み |

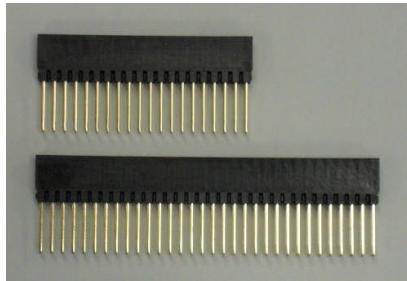

### 5.1.6 PC/104 コネクタ

PC/104 バスに使用する PC/104 コネクタのセットです。

| PC/104 コネクタセット L  |

|-------------------|

| ハンダ付けタイプ          |

| 端子長さ 23.25mm      |

| 64pin 1個 40pin 1個 |

| RoHS 対応           |

| PC/104 コネクタセット S  |

|-------------------|

| ハンダ付けタイプ          |

| 端子長さ 3.2mm        |

| 64pin 1個 40pin 1個 |

| RoHS 対応           |

### 5.1.7 インタフェースコンバータシリーズ

MS104-FPGA/C IIIにはシリアル通信用コネクタ CN2 が実装されており、シリアルインターフェース機能を実装することで弊社製インターフェースコンバータシリーズを接続してお使いいただけます。

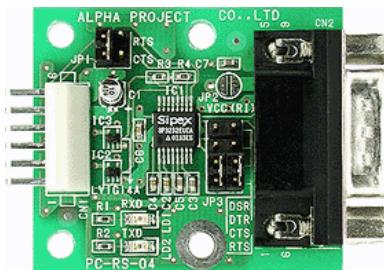

PC-RS-04

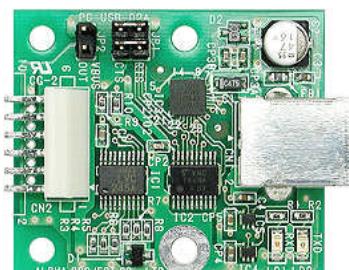

PC-USB-02A

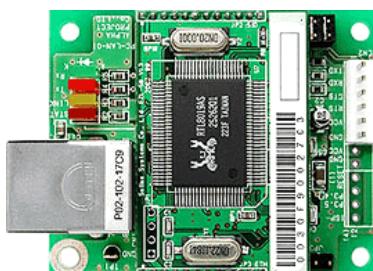

PC-LAN-01

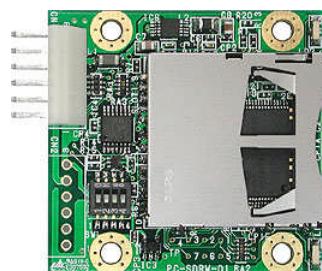

PC-SDRW-01

| 製品名        | 製品機能                |

|------------|---------------------|

| PC-RS-04   | TTLシリアル↔RS232Cコンバータ |

| PC-USB-02A | TTLシリアル↔USBコンバータ    |

| PC-LAN-01  | TTLシリアル↔LANコンバータ    |

| PC-SDRW-01 | TTLシリアル↔SDカード       |

## 6. 製品サポートのご案内

### ●ユーザ登録

ユーザ登録は弊社ホームページにて受け付けております。ユーザ登録をしていただきますと、バージョンアップや最新の情報等を E-mail でご案内させていただきまので、是非ご利用ください。

弊社ホームページアドレス <http://www.apnet.co.jp>

### ●ハードウェアのサポート

万が一、製作上の不具合や回路の機能的な問題を発見された場合には、お手数ですが弊社サポートまでご連絡ください。

以下の内容に該当するお問い合わせにつきましては受け付けておりませんのであらかじめご了承ください。

- 本製品の回路動作及び CPU および周辺デバイスの使用方法に関するご質問

- ユーザ回路の設計方法やその動作についてのご質問

- 関連ツールの操作指導

- その他、製品の仕様範囲外の質問やお客様の技術によって解決されるべき問題

### ●ソフトウェアのサポート

ソフトウェアに関する技術的な質問は、受け付けておりませんのでご了承ください。

サポートをご希望されるお客様には、個別に有償にて承りますので弊社営業までご相談ください。

### ●バージョンアップ

本製品に付属するソフトウェアは、不定期で更新されます。それらは全て弊社ホームページよりダウンロードできます。

CD-ROM などの物理媒体での提供をご希望される場合には、実費にて承りますので弊社営業までご連絡ください。

### ●修理の依頼

修理をご依頼いただく場合には、お名前、製品名、シリアル番号、詳しい故障状況を弊社製品サポートへご連絡ください。

弊社にて故障状況を確認のうえ、修理の可否、修理費用等をご連絡いたします。ただし、過電圧印加や高熱等により製品

全体がダメージを受けていると判断される場合には、修理をお断りする場合もございますのでご了承ください。

なお、弊社までの送料はお客様ご負担となります。

#### 修理・故障に関するお問い合わせ

E - M A I L

[repair@apnet.co.jp](mailto:repair@apnet.co.jp)

### ●製品サポートの方法

製品サポートについては、FAX もしくは E-MAIL でのみ受け付けております。お電話でのお問い合わせは受け付けておりま

せんのでご了承ください。なお、お問い合わせの際には、製品名、使用環境、使用方法等、問題点などを詳細に記載して

ください。

## 7. エンジニアリングサービスのご案内

弊社製品をベースとしたカスタム品やシステム開発を承っております。

お客様の仕様に合わせて、設計から OEM 供給まで一貫したサービスを提供いたします。

詳しくは、弊社営業窓口までお問い合わせください。

### 営業案内窓口

|        |                   |

|--------|-------------------|

| TEL    | 053-401-0033 (代表) |

| FAX    | 053-401-0035      |

| E-MAIL | sales@apnet.co.jp |

## 改定履歴

| 版数  | 日付         | 改定内容 |

|-----|------------|------|

| 1 版 | 2008/12/10 | 新規作成 |

## 参考文献

「Cyclone III Device Handbook」 ALTERA

その他 各社データシート

## 本文書について

- ・本文書の著作権は（株）アルファプロジェクトが保有します。

- ・本文書の内容を無断で転載することは一切禁止します。

- ・本文書の内容は、将来予告なしに変更されることがあります。

- ・本文書の内容については、万全を期して作成いたしましたが、万一ご不審な点、誤りなどお気付きの点がありましたら弊社までご連絡下さい。

- ・本文書の内容に基づき、アプリケーションを運用した結果、万一損害が発生しても、弊社では一切責任を負いませんのでご了承下さい。

## 商標について

- ・ Cyclone IIIは、ALTERA の登録商標、商標または商品名称です。

- ・ その他の会社名、製品名は、各社の登録商標または商標です。