- はじめに

この仕様書は、ATLMIRSのFPGAボード内のFPGAチップに構成するロータリエンコーダモジュールの取扱方法と機能詳細を記載したものである。

- 取扱い説明

- Maxplus2での回路情報の呼び出し方法

- ダウンロードファイル

re_m.zip

- 手順

- 圧縮ファイル re_m.zip をダウンロードします。

- re_m.zip を適当なフォルダで解凍します。

- maxplus2でグラフィックエディタを開きます。

- 解凍ファイルの中にある re_m.sym をグラフィックエディタで部品として呼び出します。

- 圧縮ファイルの内容

re_m.zip には以下のファイルが入っています。

- recont.vhd

- 機能構成図(Fig.1)に示す ラッチ回路ブロックのVHDLファイルです。

- recont.sym

- ラッチ回路のブロックシンボルです。

- re_m.acf

- モジュールのコンフィギュレーションファイル(デバイスやピン情報などが入っている)です。

- re_m.gdf

- モジュール全体のグラフフィックエディタのファイルです。

- re_m.sym

- MPCモジュール全体のブロックシンボルです。

- 機能説明

- 機能概要

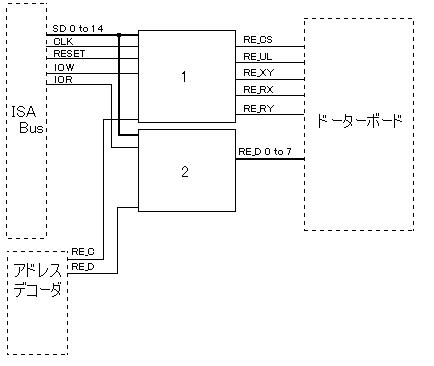

MIRSATLM FPGAボード モジュールはモータの回転数をカウントし、移動した距離の計測や自己位置を認識する行うためのものであり、FPGAボード内のFPGAチップに構成される。この機能を実現するためにMIRSATLM FPGAボード モジュールでは以下のような機能構成を持つ。

Fig.1 FPGAボード モジュールの機能構成図(re_m_block.jpg)

- ラッチ回路

この回路は、制御信号が送られてくると次に信号が来るまでその信号を保持しつづける回路。

- 出力制御回路

この回路は、データ呼出し命令がきた時にをISAバスにチップのデータを送る機能を持つ。

- 機能詳細

機能詳細では、機能構成図(Fig.1)に示した各機能ブロックの詳細説明を行う。

- ラッチ回路

この回路はアドレスが指定されるとアドレスデコーダから発生する"RE_C"がH、バスの書きこみ命令である"/IOW"のがLとなると、そのときにデータバスに送られてきているデータを次にデータが送られてくるまで保持する。

また、その送られてきたデータ次のデータが来るまでを出力RE_UL,RE_XY,RE_CS,RE_RX,RE_RYに次のデータが来るまで送りつづける。この信号は、μPD4701のチップに送られて、このチップを制御する。

- 出力制御回路

この回路は、アドレスが指定されるとアドレスデコーダから"RE_D"にHが送られていて、バスの読み取り命令である"IOR"にLが送られている間、ISAバスのデータバスにμPD4701から送られた信号をISAバスに送る。

それ以外の場合は、ハイインピーダンスを出力しておく。

- 信号の詳細

信号の詳細では、MIRSATLM FPGAボード *モジュール内で使用されている各信号の詳細説明を行う。

- RE_C

この信号はロータリエンコーダの値を読み取るのに必要な制御信号を送り出すアドレスが選ばれたときにこのモジュールを選択するための信号である。

- RE_D

この信号はロータリーエンコーダの値を読み取るアドレスが選ばれたときこのモジュールを選択するための信号である。

- SD 0 to 15

この信号はデータ読取信号をISA‐Busに送ったり、読取制御命令信号をISA-Busから読み込んだりするために使う、データのやり取りの信号である。

- IOR

この信号はISA‐BusのI/Oリード・ストローブである。

- IOW

この信号はISA‐BusのI/Oライト・ストローブである。

- RESET

この信号はISA‐Busのシステム・リセットである。

- CLK

この信号はISA-Busのシステム・クロック 8MHz デューティ50%である。

- RE_CS

この信号はμPD4701を制御する信号でチップセレクトである。これがLowレベルになるとロータリエンコーダのカウント値がラッチされる。そのため読み込みしてるときはずっとLowを保持しなければいけない。

- RE_XY

この信号はμPD4701の制御信号でXカウンタ・Yカウンタ選択をする。HiでYカウンタをLowでXカウンタを選択します。

- RE_UL

この信号はμPD4701の制御信号でカウントデータ上位・下位選択をする。Hiで上位バイトをLowで下位バイトを選択します。

- RE_RX

この信号はμPD4701の制御進号でXカウンタリセットをする。Hiでアクティブとなる。

- RE_RY

この信号はμPD4701の制御進号でYカウンタリセットをする。Hiでアクティブとなる。

- RE_D 0 to 7

この信号はμPD4701からくるカウントデータ信号である。RE_XY及びRE_ULによって選択されたバイトデータがμPD4701から送られてくる。

- インターフェース

Table 1 ロータリエンコーダモジュールのインターフェース

信号名

|

方 向

|

対 象

|

概 要

|

RE_C

|

IN

|

アドレスデコーダ |

モジュールセレクタ信号(動作制御命令用)

|

RE_D

|

IN

|

アドレスデコーダ |

モジュールセレクタ信号(データ読取用)

|

SD 0 to 15

|

IN

|

ISA-Bus |

16bit データバス

|

IOR

|

IN

|

ISA-Bus |

I/Oリード・ストローブ

|

IOW

|

IN

|

ISA-Bus |

I/Oライト・ストローブ

|

RESET

|

IN

|

ISA-Bus |

システム・リセット

|

CLK

|

IN

|

ISA-Bus |

システム・クロック 8MHz デューティ50%

|

RE_CS

|

OUT

|

ドーターボード |

チップセレクト

|

RE_XY

|

OUT

|

ドーターボード |

Xカウンタ・Yカウンタ選択

|

RE_UL

|

OUT

|

ドーターボード |

カウントデータ上位・下位選択

|

RE_RX

|

OUT

|

ドーターボード |

Xカウンタリセット

|

RE_RY

|

OUT

|

ドーターボード |

Yカウンタリセット

|

RE_D 0 to 7

|

IN

|

ドーターボード |

カウントデータ

|

|

|