|

名称 |

MIRS0803 FPGA製造仕様書 |

||||

|

番号 |

MIRS0803-ELEC-0002 |

||||

|

版 数 |

最終更新日 |

作 成 |

承 認 |

改 訂 記 事 |

|

|

A01 |

2008/12/1 |

大石 |

鈴木 |

初版 |

|

|

A02 |

2009/02/24 |

大石 |

鈴木 |

詳しい送信データと応答を追加 |

|

|

|

|

|

|

|

|

1.FPGAの変更点

標準機のFPGA回路データを基に以下の変更を加える。

・ GDC(Galactic a Daunts Control)送信回路の作成

・ アドレスデコーダの変更

・ ピン割り当て変更

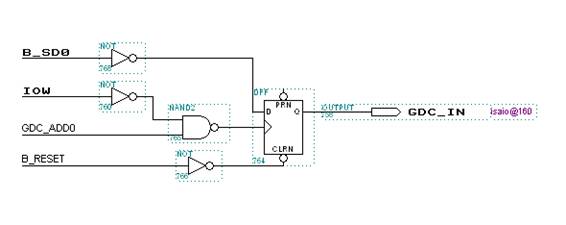

2GDC送信回路

160番地を指定したとき、160ピンに信号を送信する回路を作成。

下図のGDC_ADD0はアドレスデコーダからの出力である。

MIRS本体からは160番地に0x0001と0x0000が送信される。

0x0001が送信されたとき出力1、0x0000が送信されたとき出力0がでるようになっている。

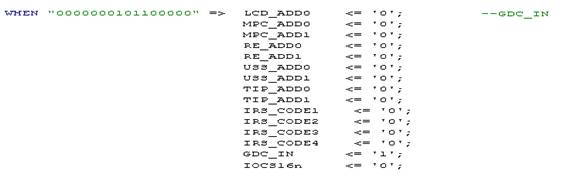

3.アドレスデコーダの変更点

add_doc.vhdの内部に160番地を指定したときに”1”が出力される回路を加える。

4.ピン割り当て変更

GD制御回路への送信信号はIRS1を使用するため、標準機回路のIRS1のピン割り当てを解除し、GDC送信回路のoutputにピン番号160を割り当てる。