|

沼津高専 電子制御工学科 |

||||||

|

||||||

|

改訂記録 |

||||||

|

版数 |

作成日 |

作成者 |

承認 |

改訂内容 |

||

|

A01 |

2007.2.18 |

藤田・齋藤 |

平田 |

初版 |

||

目次

1 概要

2 ピン割り当て

3 詳細な設計

4 注意点

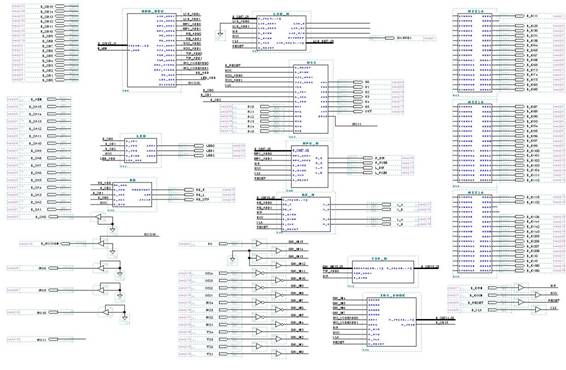

まず最初にMIRS0702の設計したFPGAデータを掲載する→FPGA0702

主な変更点は以下の通りである。

・

ISAIO.GDF上のoutputのLCD_DB1~7を削除。同時にピンの割り当ても削除。

・

ISAIO.GDF上のLCD_Mの入力のNODEのLCD_ADD0にGNDを接続。

・

ISAIO.GDF上のADD_DECの出力NODEの名前LCD_ADD0をLCD_ADDxに変更

・

add_dec.vhdのIRS_CODE3をRB_ADDに置換し、シンボルの出力からRB_ADDというNODEを出す。更に同様にしてIRS_CODE4をLED_ADDに置換してNODEをだす。

・

uss.gdf内で使われているencoder.vhdを変更。入力Dを3bitにし、出力Xを6bitに変更。uss.gdf内のinputにB_SD2、RV4、RV5を、outputにSA4、SA5を追加。既存のものを参考に接続。シンボルの出力にinput、outputピンを接続する。

・

新たにシンボルRBを設計。inputはRB_ADD, B_SD0, B_SD1, B_SD2, B_IOW,とする。outputはRIGHTGHT, LEF, STOOPとする。

・

RBをシンボル化してISAIO.GDFに配置。新たにoutputピンを作成し、RB_R, RB_L, RB_STPとしてrbのそれぞれの出力に接続する。

・

新たにシンボルLEDを設計し、入力にB_SD0~2、IOW、LED_ADDを、出力にoutputピンのLED0~2を接続する。

標準MIRSと比べ変更した点を示す。

input

RV_4 177

RV_5 175

output

LCD_DB1~7 削除

RB_R 187

RB_L 190

RB_STP 189

U4 176

U5 174

LED0 193

LED1 192

LED2 191

Ⅰ.ISAIO.GDF

LCD_ADD0にGNDを接続したのは、LCDを使用しないのでLCD_Mのモジュールが動作しないようにするためである。GNDを接続するのに伴い、ADD_DECの出力であるLCD_ADD0の名前をLCD_ADDxにすることでコンパイルエラーが発生しないようにした。

Ⅱ.ADD_DEC.vhd

LIBRARY

ieee;

USE

ieee.std_logic_1164.all;

ENTITY

ADD_DEC IS

PORT

(

SA :

IN STD_LOGIC_VECTOR(15

DOWNTO 1);

B_AEN :

IN STD_LOGIC;

LCD_ADD0,LCD_ADD1 : OUT STD_LOGIC;

MPC_ADD0,MPC_ADD1 : OUT STD_LOGIC;

RE_ADD0,RE_ADD1 :

OUT STD_LOGIC;

USS_ADD0,USS_ADD1 :

OUT STD_LOGIC;

TIP_ADD0,TIP_ADD1 :

OUT STD_LOGIC;

IRS_CODE1 :

OUT STD_LOGIC;

IRS_CODE2 :

OUT STD_LOGIC;

RB_ADD :

OUT STD_LOGIC;

LED_ADD :

OUT STD_LOGIC;

IOCS16n :

OUT STD_LOGIC

);

END

ADD_DEC;

ARCHITECTURE

DATAFLOW OF ADD_DEC IS

signal

add : std_logic_vector(15 downto

0);

BEGIN

add

<= SA & B_AEN;

LCD_ADD1

<= SA(1);

PROCESS

(SA,B_AEN)

BEGIN

CASE

add IS

WHEN

"0000000100000000"

|"0000000100000010"

=> LCD_ADD0

<= '1';

MPC_ADD0

<= '0';

MPC_ADD1

<= '0';

RE_ADD0 <=

'0';

RE_ADD1 <=

'0';

USS_ADD0

<= '0';

USS_ADD1

<= '0';

TIP_ADD0

<=

'0';

TIP_ADD1

<=

'0';

IRS_CODE1 <= '0';

IRS_CODE2 <= '0';

RB_ADD <= '0';

LED_ADD <= '0';

IOCS16n

<=

'1';

中略

WHEN

"0000000101010100"=> LCD_ADD0

<= '0';

MPC_ADD0

<= '0';

MPC_ADD1

<= '0';

RE_ADD0 <=

'0';

RE_ADD1 <=

'0';

USS_ADD0

<= '0';

USS_ADD1

<= '0';

TIP_ADD0

<=

'0';

TIP_ADD1

<=

'0';

IRS_CODE1 <= '0';

IRS_CODE2 <= '0';

RB_ADD <= '1';

LED_ADD <= '0';

IOCS16n

<=

'1';

WHEN

"0000000101010110"=> LCD_ADD0

<= '0';

MPC_ADD0

<= '0';

MPC_ADD1

<= '0';

RE_ADD0 <=

'0';

RE_ADD1 <=

'0';

USS_ADD0

<= '0';

USS_ADD1

<= '0';

TIP_ADD0

<=

'0';

TIP_ADD1

<=

'0';

IRS_CODE1 <= '0';

IRS_CODE2 <= '0';

RB_ADD <= '0';

LED_ADD <= '1';

IOCS16n

<=

'1';

WHEN

OTHERS => LCD_ADD0

<= '0';

MPC_ADD0

<= '0';

MPC_ADD1

<= '0';

RE_ADD0 <=

'0';

RE_ADD1 <=

'0';

USS_ADD0

<= '0';

USS_ADD1

<= '0';

TIP_ADD0

<=

'0';

TIP_ADD1

<=

'0';

IRS_CODE1 <= '0';

IRS_CODE2 <= '0';

RB_ADD <= '0';

LED_ADD <= '0';

IOCS16n

<=

'0';

END

CASE;

END

PROCESS;

END

DATAFLOW;

以上のように変更した。

この回路はCPU側から送られてくる16進の4桁の信号を2進16桁の値に直し、その値によってどのモジュールを動かすのかを決定するための回路である。

ISAIO.gdfをみてIRS_CODE3とIRS_CODE4は標準MIRSでは使用していないことはわかっていたし、自分たちも赤外線センサを増やす予定はないのでIRS_CODE3をRB_ADDと名前を変更して使用することにした。

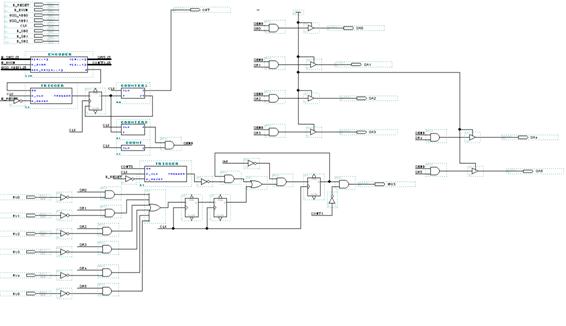

Ⅲ.uss.gdf

以上のように変更した。変更に伴い、シンボルENCODERの中身も変更したのでencoder.vhdを以下に示す。

LIBRARY

ieee;

USE

ieee.std_logic_1164.all;

USE

ieee.std_logic_arith.all;

ENTITY

ENCODER IS

PORT

(

D :

IN STD_LOGIC_VECTOR(2

downto 0);

B_IOWN : IN STD_LOGIC;

ADD_DEC :

IN STD_LOGIC_VECTOR(1

downto 0);

X :

OUT STD_LOGIC_VECTOR(5 downto 0);

Y :

OUT STD_LOGIC_VECTOR(1 downto 0);

Z :

OUT STD_LOGIC);

END

ENCODER;

ARCHITECTURE

RTL OF ENCODER IS

SIGNAL B :

STD_LOGIC;

SIGNAL C :

STD_LOGIC;

begin

C

<= ADD_DEC(0) and not B_IOWN;

B

<= ADD_DEC(1) and not B_IOWN;

Z

<= C;

process(C,B)

begin

if

(C'event and C='1') then

case

D is

when

"000" => X <= "000001";

when

"001" => X <= "000010";

when

"010" => X <= "000100";

when

"011" => X <= "001000";

when

"100" => X <= "010000";

when

"101" => X <= "100000";

when

others =>

X <= "000000";

end

case;

end

if;

if

(B'event and B='1') then

Y(1)

<= D(1);

end

if;

end

process;

Y(0)

<= D(0) and B;

end

RTL;

内容について触れると、uss.gdfに入ってくるB_SDの3bitの信号をDにいれて、その値によってXに入れる値を変化させることで、どの超音波センサを動かすのかを決めている。

encoder.vhd内の内部信号B,Cはそれぞれ、送信信号の送信、割り込み処理用信号として使われている。

超音波センサは送信信号を出してから、割り込み信号のIRQ3を受信するまでの時間を測定することで距離を計算しているので、割り込み用の信号などが他の回路などに比べ増えている。

uss.gdfの下側にある回路は、割り込み信号を作るための回路であるが、超音波を出しているときに回り込んで入ってくる音波を受信しないようにするマスクをするための回路が組み込まれている。

uss.gdf内のoutという信号は、超音波センサのマスク用の信号と思われる。

個人的見解であるが、他のモジュールと比べ、IORの入力がないのが目に付くが、これは割り込みによってCPUに値を返しているで、バスのREADは行われないためであると考える。

また、今回はいじっていないが、triggerの回路は3年の計算機で学習した微分回路になっている。勉強した知識が役に立つとうれしいものだ。

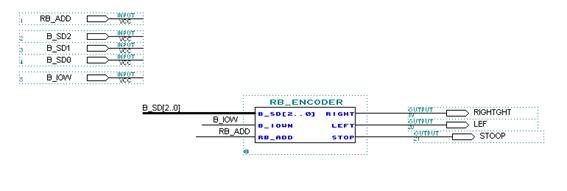

Ⅳ.RB.gdf

このモジュールはMIRS0702が新たに開発した部分である。

この中のRB_ENCODERも自作したので示す。

LIBRARY

ieee;

USE

ieee.std_logic_1164.all;

USE

ieee.std_logic_arith.all;

ENTITY

RB_ENCODER IS

PORT

(

B_SD : IN STD_LOGIC_VECTOR(2 downto 0);

B_IOWN : IN STD_LOGIC;

RB_ADD :

IN STD_LOGIC;

RIGHT : OUT STD_LOGIC;

LEFT : OUT STD_LOGIC;

STOP : OUT STD_LOGIC);

end

RB_ENCODER;

ARCHITECTURE

RTL OF RB_ENCODER IS

SIGNAL C :

STD_LOGIC;

begin

C

<= RB_ADD and not B_IOWN;

process(C)

begin

if(C'event and C='1') then

STOP

<= B_SD(0);

RIGHT

<= B_SD(2);

LEFT

<= B_SD(1);

end

if;

end

process;

end

RTL;

RB_ENCODER内では特別なことはしていない。一部uss.gdf内で使われているENCODERを参考にして作成した。アドレスデコーダの値が立ち上がるのをクロックにしてB_SDの値を代入しているので、USSを動かすなどの他の処理をしてB_SDの値が変更されても、次にRB_ADDが立ち上がるまで値は保持される。B_SDは回転盤制御以外の動作をすると変化してしまうため、値を保持しておくことは重要である。

Ⅴ.LED.vhd

LED制御用に新規に作成したシンボルのVHDLの内容を示す。

LIBRARY

ieee;

USE

ieee.std_logic_1164.all;

USE

ieee.std_logic_arith.all;

ENTITY

LED IS

PORT

(

B_SD0 : IN STD_LOGIC;

B_SD1 : IN STD_LOGIC;

B_SD2 : IN STD_LOGIC;

B_IOWN : IN STD_LOGIC;

LED_ADD :

IN STD_LOGIC;

LED0 : OUT STD_LOGIC;

LED1 : OUT STD_LOGIC;

LED2 : OUT STD_LOGIC);

END

LED;

ARCHITECTURE

RTL OF LED IS

SIGNAL C :

STD_LOGIC;

begin

C

<= LED_ADD and not B_IOWN;

process(C)

begin

if(C'event and C='1') then

LED0

<= B_SD0;

LED1

<= B_SD1;

LED2

<= B_SD2;

end

if;

end

process;

end

RTL;

これもRBと同様の処理をしているため説明は省略する。

4.注意点

MIRSのFPGA回路の設計ではMAX+plusⅡを用いて設計している。このソフトは3年の計算機工学で用いたQuartusと同じAltera社のソフトであるが、互換性はないため、Quartusでは編集もとい開発することができないのでFPGAの回路を変更する際にはMAX+plusⅡを使わなければならない。

MAX+plusⅡを使う上での注意点であるが、まずマウスのホイールによるスクロールはできない。またgdfファイル(Graphic

Editor file)では作業領域が限られているので上手くやりくりしなければならない。

また、Quartusとの決定的に違う点として、プロジェクトファイルが存在しない。プロジェクトを開くときは、メニュー>file>Project>Nameから編集したいファイルを開くことで、そのファイルのプロジェクトを開くことができる。よってそのようにプロジェクトを開いた上でfile>openやfile>Newで開発するようにしなければならない。

また、シンボルを新たに作るときや、既存のシンボルを一部変更するときには、file>Create Default Symbolを実行してからSymbol>Update

Symbolを実行しないと変更が反映されないので注意すること。